LVDS技术在数字视频传输系统中的应用

随着信息技术的发展,多媒体、虚拟现实以及网络技术对数字视频信号的带宽要求越来越大,数据传输的需求急剧增加。包含丰富信息量的视频图像传输技术倍受关注。传统的视频传输方法在速度、噪声、EMI/EMC、功耗、成本等方面存在很大的局限性。因此,采用新的I/O接口技术来解决视频图像传输问题显得日益突出。低电压差分信号传输技术简称LVDS(Low Voltage Differential Signal)技术具有高速、低成本的特性为解决视频传输这一瓶颈问题提供了可能。

LVDS技术核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,远距离信号传输。具有低功耗、低误码率、低串扰和低辐射等特点。其传输介质可以是铜质的PCB连线,也可以是平衡电缆。LVDS技术是种低摆幅的通用I/0标准,其低摆幅和低电流驱动输出实现低噪声和低功耗,解决物理层点对点传输的瓶颈问题,满足数据高速传输的要求。

将LVDS技术应用到数字视频传输系统中,通过合理的方案设计使系统能满足图像数据实时、稳定、高速传输的要求。

1 数字视频传输系统硬件设计

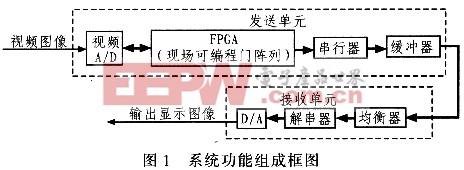

数字视频传输系统由发送单元和接收单元组成,其功能组成框图见图1。发送单元主要由FPGA、A/D转换器、串行器和信号预加重缓冲器组成,主要完成模拟视频信号数字化和数字图像信息串行经驱动后发送给接收单元。接收单元主要由LVDS均衡器、解串器和D/A组成,主要完成串行差分信号的解串,恢复成并行的数字信号信息,并将解串后的信号经D/A转换为模拟视频信号。

1.1 FPCA(现场可编程门阵列)

方案采用Actel公司推出的第二代基于Flash(闪存)的可编程器件ProASIC Plus系列中的APAl50。该系列器件具ASIC(专用集成电路)的性能和FPGA的灵活性于一身,具有150 000个系统门.逻辑单元为6 144个,内嵌36 Kb的双端口SRAM和2个锁相环(PLL)内核,支持3.3 V、32 bit、50 MHz的PCI总线,系统外部性能达150 MHz,具有高密度、低功耗、非易失及可重复编程等特点。因为ProASIC Plus系列FPGA基于Fla-sh技术,利用Flash开关保存内部逻辑,因此不需要另外的器件。由于不需要上电配置过程,因此具备上电就立即工作的特点。另外高度保密,使用者可编程设置多位密钥以阻止外界自行读取或更改器件的配置。方案中利用APAl50主要实现逻辑控制、A/D采样控制、数字图像增强等功能。

1.2 LVDS接口电路设计

LVDS接口电路由串行/解串器、预加重器和均衡器等组成,主要负责LVDS信号的转换和传输,是整个系统设计的关键。图2是系统LVDS接口电路连接图,其中串行器DS92LV18将FPGA输出的图像数据和有关图像的时钟和同步信号等并行信号转换为串行LVDS信号输出,经DS25BRl20接口器件预加重后,传输给接收单元的均衡器器件DS25BRll0,均衡后的LVDS信号再通过解串器DS92LV18恢复成并行信号送D/A转换器进行数/模转换。

评论