触摸屏控制器芯片中的高精度低功耗ADC设计

摘要:鉴于市场上现有触摸屏控制器功耗较大,而ADC是触摸屏控制器的核心电路,本文设计了采用睡眠/唤醒两种工作模式工作的ADC电路。有触摸事件时,ADC开启且不需唤醒延时,否则处于睡眠状态。根据寄生容值,本文对DAC级间耦合电容进行了优化设计,大大提高了ADC精度。实践表明:该芯片可在2.5 V ~5.3V 电压范围、-40 °C ~85 °C 温度范围下工作,芯片功耗不足1mW,且均可达到12位精度。电路具有精度高、功耗低、版图面积小的特点,对触摸屏控制器的优化设计有指导作用。

关键词:开关电容网络; 逐次逼近模数转换器; 耦合电容; 比较器

引言

ADC 采用逐次逼近型(SAR)结构,具有125kHz采样速率,12位精度。电容电荷重新分布D/A技术采用电荷按比例缩放子DAC组合,进而大大减小了芯片电容面积,也避免了采用像电阻阵列结构所带来的固有直流功耗,通过对DAC级间耦合电容值的优化设计,提高了ADC精度。比较器采用自消除失调电压的开关电容比较器。

据调研,市场上现有触摸屏控制器芯片主要来自ADI公司(如AD7843、AD7873、AD7877)和TI公司(如ADS7843、TSC2046、TSC2003),对其性能进行对比,如表1所示。

表1触摸屏控制器芯片性能对比结果

通过对ADC电路进行优化设计,可使触摸屏控制器的功耗不足1mW,低于表1中现有芯片的功耗。

因此本设计的侧重点是在满足工作电压、工作温度的基础上,使ADC工作在睡眠/唤醒两种工作模式下,以大大降低功耗。为了实现这一目的,芯片中设计了电压基准电路模块,以控制ADC的开启和关闭。

电路设计与分析

ADC的整体结构设计

SAR ADC包括采样保持电路、比较器、DAC、逐次逼近寄存器、时序产生及数字控制逻辑电路。模拟输入电压(vin)由采样/保持电路保持,N位SAR ADC需要N个比较周期,同时在当前一位转换完成之前不得进入下一次转换。因此该类ADC能够有效节省功耗和空间,该结构中DAC和比较器设计的好坏对整个ADC转换精度起关键性的作用。

DAC的设计

DAC结构设计

由于在CMOS集成电路中,制造电容比制造电阻更节省芯片面积,而且电容上没有功率损耗,另外,开关电容网络可以完成采样保持的功能,节省了单独的采样保持电路。因此,本文选择采用开关电容网络构成电荷按比例缩放式DAC。

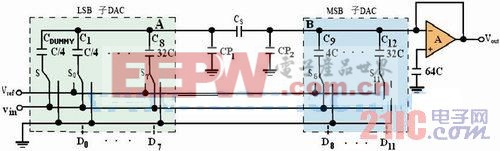

电荷按比例缩放式DAC主要由按照二进制加权排列的电容阵列组成。电容是CMOS工艺兼容的,而且相对精度高,所以电荷按比例缩放式DAC在CMOS工艺中容易实现。然而当其精度提高时,一方面所需的大电容导致芯片尺寸过大,而且大电容需要大充电电流,充电时间过长;另一方面最高权位和最低权位的电容比例变得很大,比值越大,电容匹配越差。所以高精度DAC通常由低精度DAC通过电容耦合来实现。这种耦合结构成功的关键之一是确定耦合电容值。只有选择合适的耦合电容值,才能保证各位间的权重关系,并实现D/A转换,如图1所示。

图1 电荷按比例缩放式DAC组合的实现

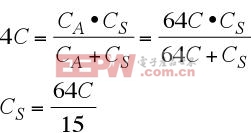

设图1中A点到地的电容为CA,DAC的缩放通过电容CS实现,CS和LSB阵列的串联组合必须接于MSB阵列的左侧,因此可得:

版图设计时,为了消除介电松弛对转换精度的影响,消除电荷扩散和介电极化效应,减少噪声干扰,电容上极板上会加静电屏蔽层,并接地。为了消除衬底噪声,将电容做在阱里,阱接地。电容阵列极板和屏蔽层或阱间形成的寄生电容,使电路中耦合电容两极板地的寄生电容值增大,使得在确定耦合电容值时,必须考虑寄生电容的影响。

评论