基于Spartan-6的16路高速串行传输的设计与实现

2.2 OSERDES

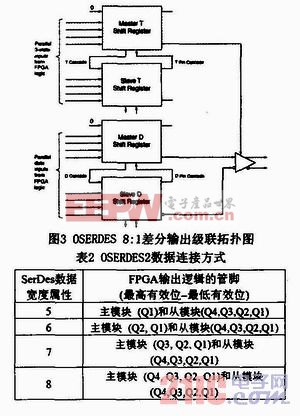

同样,每一款Spartan-6型号FPGA的IOB的输出SerDes都可以用OSERDES2源语来实例化。其结构和源语操作方式以及转换速率比与ISER-DES2源语类似,在SDR模式下,可以实现1bit串行数据到生成2、3、4bit的并行数据的转换;在差分输出方式下,可以实现1bit串行数据到5、6、7及8bit并行数据的转换。下图为OSERDES2模块以8:1的转换率配置下差分输出的级联图。

图3 OSERDES 8:1差分输出级联拓扑图本文引用地址:http://www.eepw.com.cn/article/162171.htm

当两个OSERDES2级联时,其中一个是主模式,一个是从模式,表2显示了两个OSERDES2源语级联时的数据位高低连接方式

3 Spartan-6的1 6路高速串行传输的设计

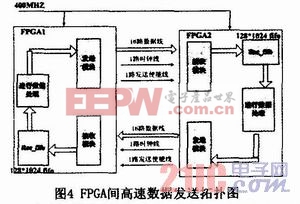

两片XC6SLX150 FPGA之间以16路高速数据相互通信,其中还需要一路源同步时钟,一路标志信号用来使能片间数据的收发控制,每片FPGA需要一个400MHz的时钟输入作为高速数据发送时钟。其基本的发送拓扑图如下:

接收时钟直接使用源同步时钟,发送时钟采用输入到FPGA的400MHz的时钟。接收的数据送到一个128×1024的fifo中,然后进行处理,将数据送到发送模块,发送给相连的FPGA中,另一片FPGA做同样的处理。

3.1 发送模块

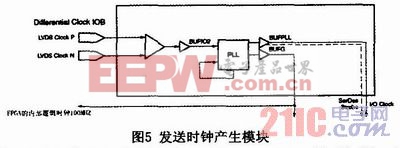

发送模块采用输入到FPGA的400MHz的时钟作为发送时钟源,首先经BUFI02后送入PLL,产生一个800MHz的采样发送时钟和一个100MHz的FPGA内部逻辑时钟,再通过一个BUFPLL驱动用于后续的逻辑。发送时钟的产生模块如图5所示。

评论