基于DVI接口的图像总线控制系统

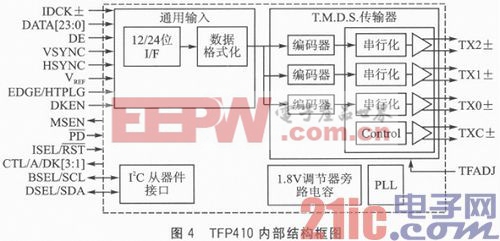

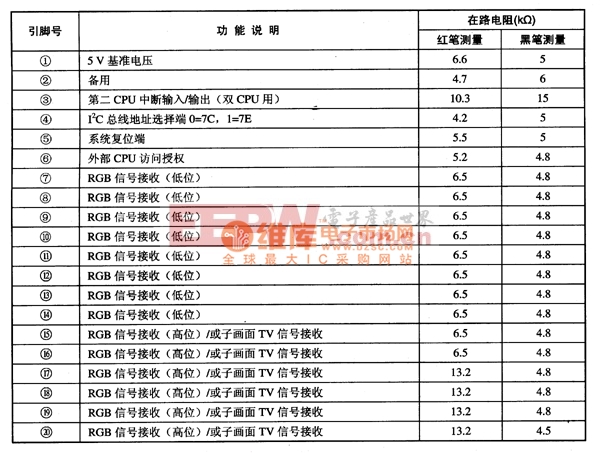

系统采用TI公司的视频编码芯片TFP410,编码后的TMDS信号通过DVI电缆传送至DVI显示器。与TFP401对应,TFP410支持从VGA到UXGA(25~1 65MHz)格式的像素速率,具有12位双边和24位单边两种输入模式,可以通过I2C总线进行芯片工作模式配置。TFP410主要通过DE引脚的高低电平来决定发送信号类型:当DE为高电平时,发送像素编码数据;当DE为低电平时,发送同步信号以及控制信号。ISEL引脚的高低决定是否采用I2C总线,ISEL信号为低电平时,需要根据外部引脚对芯片进行配置;当ISEL信号为高电平时,可以通过I2C总线来配置,此时外部引脚配置不起作用。TFP410内部结构框图如图4所示。本文引用地址:http://www.eepw.com.cn/article/159314.htm

4 CAN总线通信模块

系统需要和上位机进行通信,采用CAN总线进行数据交互。CAN总线具有通信速率高、开放性好、报文短、纠错能力和扩展能力强的特点,通信速率可高达1 Mbps,特别适用于实时性要求很高的网络。

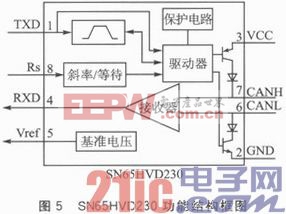

系统采用了集成CAN总线控制器的C8051F系列单片机。通信软件设计通过KeilC51实现,程序分别实现单片机交叉开关配置与端口初始化、外部振荡器初始化、CAN总线定时寄存器初始化、消息对象初始化、CAN总线数据发送和接收、消息响应、错误处理、系统广播等功能。SN65HvD230功能结构框图如图5所示。

采用TI公司生产的3.3 V芯片SN65HVD230作为总线收发器。该收发器与PCA82C250引脚兼容,具有差分收发能力、高速率传输(1 Mbps)、高抗电磁干扰、超小封装、低功耗等性能;并有3种不同工作模式可供选用,与集成了CAN总线控制器的C8051F系列单片机配合使用,可使外围电路更加简洁。

SN65HVD230的CANH和CANL输出引脚需并联一个电阻,作为CAN总线的终接电阻,终接电阻需满足传输电缆的特性阻抗,一般取值120 Ω。

SN65HVD230的Rs引脚为斜率电阻输入引脚,通过改变加在该引脚上的电压,可以改变收发器的工作方式。

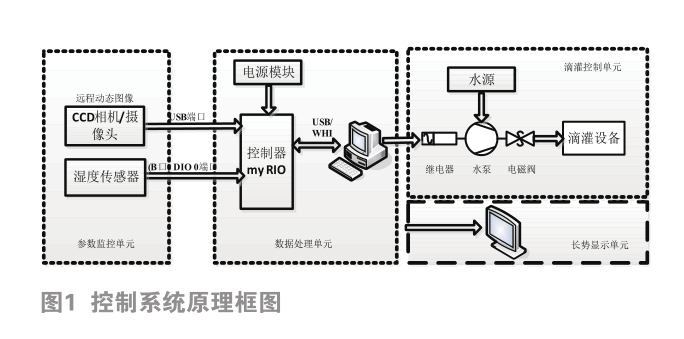

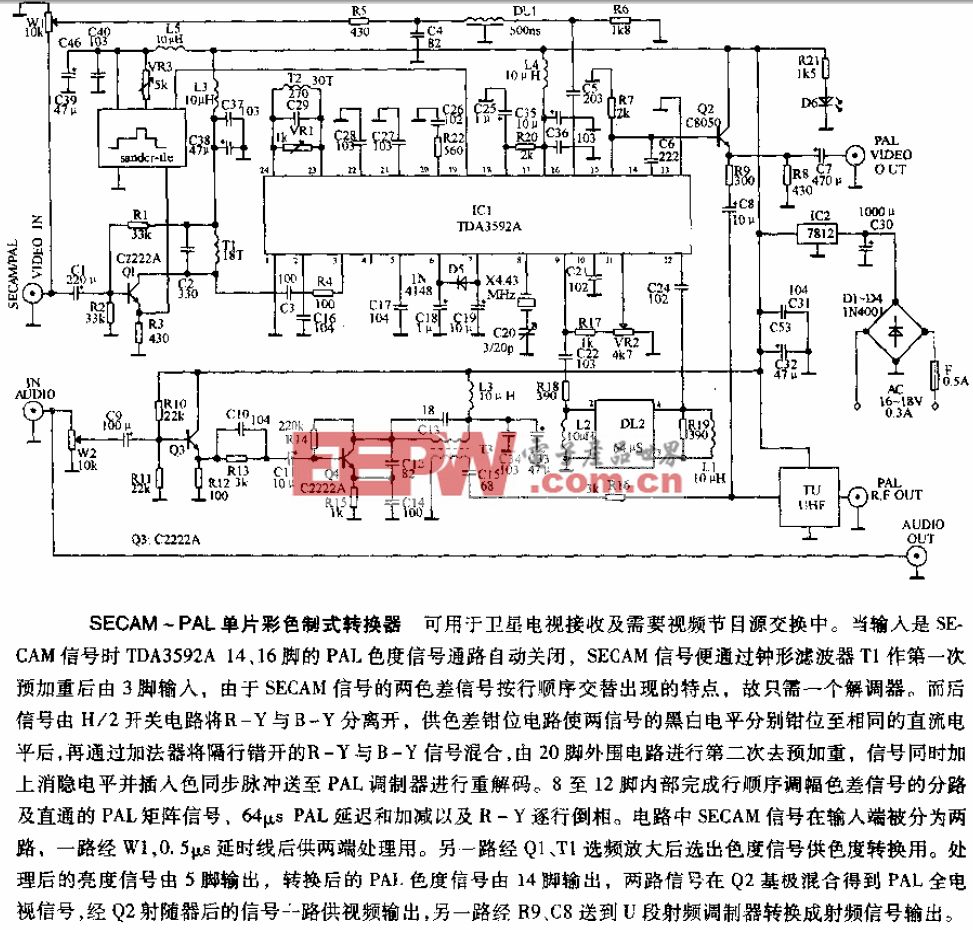

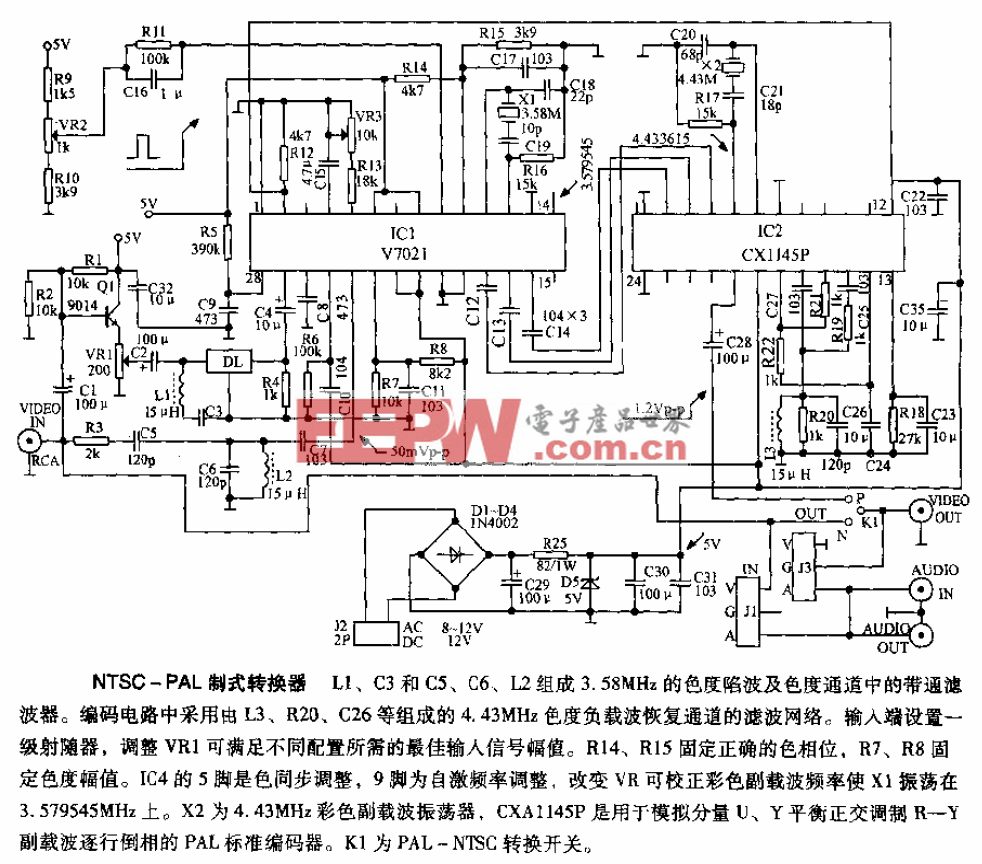

5 PAL模块

系统提供一路PAL制式模拟信号输出给TV监视器。由于PAL制式场频为50Hz,帧频为25 Hz,所以前端高分辨率高帧频的数字图像必须降频输出,且分辨率也要降低。PAL编码芯片选用Philips公司生产的SAA7128,支持PAL/NTSC/SECAM制式的编码。它可以接受ITU-R BT.656格式4:2:2数据流信号,输出标准CVBS复合视频信号。

SAA7128将FPGA送出来的ITU-R BT.656格式4:2:2数据流进行数模转换,经过视频矩阵编码转换成模拟的视频信号。该芯片工作在SLAVE模式下,即27MHz数据时钟由外部振荡器供给。SAA7128利用此时钟对数字信号进行锁存。

系统选用的C8051F系列单片机具有I2C总线功能。可通过I2C总线对SAA7128上电后进行初始化控制。PAL信号的HS行同步,VS场同步信号均由SAA7128自动生成。

FPGA首先在内部建立一个RGB信号到YCbCr信号的转换表。可在FPGA内部开辟两片RAM进行乒乓操作,FPGA利用HS行同步、VS场同步来组成ITU-RBT.656格式4:2:2的数字视频流。PAL一帧传递结束时,置一个标志位,SAA7128开始读其中一片RAM的数据,同时对另一片RAM进行写操作,写入一帧新的数据,如此往复。并使TV监视器能够看到完整的CVBS信号图像。在FPGA设计时,必须注意PAL信号分奇偶场,采集的信号需要隔行采集,两场结束才为完整的一帧图像。

结语

本文从工程应用的角度出发,详细介绍了基于DVI接口的图像总线控制系统,该系统能够采集基于Camlink接口的高速CCD传送的数字视频信号,并能通过DVI接口实现1080 P的高清显示。实践证明,该系统采集数据稳定、图像清晰,具有较高应用价值,可广泛应用于图像处

理领域。

评论