基于同轴与光纤结合的2km数据传输的设计

摘 要:若采用没有信号调节功能的LVDS芯片与设有驱动器预加重功能和接收器均衡功能的LVDS集成电路构成系统传输数据,电缆的长度便可最多到数百米。但这些系统想要进行数十公里长距离的数据传送,便应将LVDS信号经过光模块转成光信号来传输,并将之与LNDS系统一起搭配使用。采用DS92LV1023和lDS92LV1224型号的LWDS芯片与驱动芯片CL006和CLCOl4相互配合构成LVDS系统,再与光模块构成一个大系统便能够传输数十公里的距离。该系统已投入使用,其性能可靠、稳定、支持。

关键词:LVDS芯片:长距离;同轴电缆:光模块.

0 引言

随着各式各样的接入通信设备的应用,数据传输的需求急剧增加。设备的电路系统必须提高传输的速度,设备采用LVDS技术,使其传输速度高达数百Mbps。但是,LVDS的出现只能满足短距离(不超过几米)传输条件下数据高速传输的要求。自适应均衡器可自动为信号损耗提供补偿,使电缆传来的串行数字信号可以重新恢复其原有强度。利用这一特点采用高速串行数字接口(SDI)自适应电缆均衡器及电缆驱动器芯片构建系统,可以扩大LVDS技术的数据传送范围到二、三百米。

随着通信技术的飞速发展,光纤通信已成为通信的重要手段。光纤传输系统具有容量大,传输距离远,抗干扰性强等优势,在通信传输方面有着不可替代的地位,目前,单模光纤能以1.2Gbyte/s的速度传输20km。综合以上两个特点采用LVDS芯片与光模块构建系统,可以在特殊环境下扩大数据传送范围,以满足高速率条件下长距离传送的要求。

在导弹上面的电缆网有好几级托插件构成,如果用光纤接口做托插件的话需要外围电路,并且光模块本身体积也很大,由于导弹上的空间有限,所以在导弹上面用光纤不合理。同轴电缆则不存在这样的问题,它通过标准SMA接插件就可以连接起来,SMA接插件比同轴电缆少粗一点,几乎不占体积。因此,本文采用的就是高速串行数字接口(SDI)自适应电缆均衡器及电缆驱动器芯片与LVDS芯片搭配构成弹上系统,在地面上采用光模块将LNDS信号转成光信号传输2km。整个系统主要完成导弹飞行前的实时检测过程中的数据传输。

1 总体方案设计

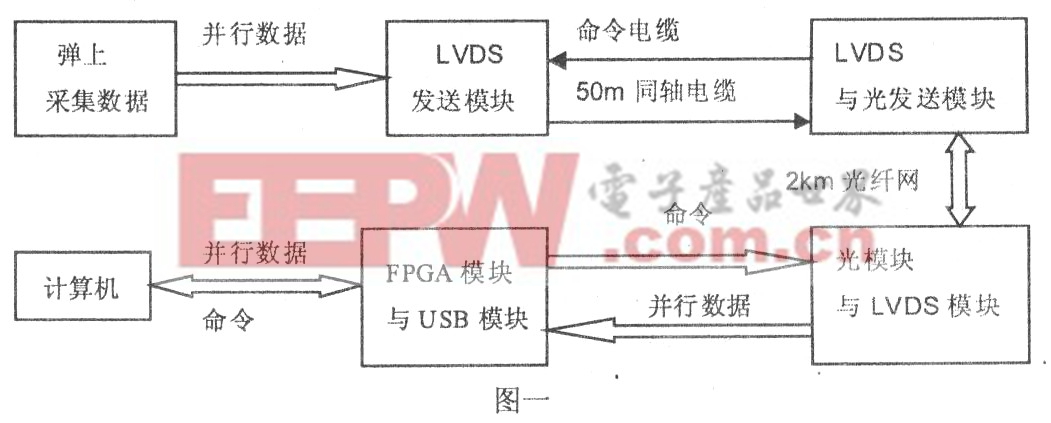

本系统需要完成在100Mbps速度情况下数据的传输,传输距离为2km。并且需要光信号与电信号的转换问题。因此,在满足传输速度为100Mbps的条件下,主要考虑的是数据的传输距离的问题。也就是说,需要解决两方面的问题:(1)延长传输距离的问题(2)速度匹配问题。图一为系统原理框图。其中,导弹上的采编器采集到的数据通过LVDS发送模块转成串行数据,再经过50m的同轴电缆传到地面上的LVDS模块与光模块组合而成的模块,这个组合模块是收发一体的模块。在地面上通过收发一体的模块将电信号转成光信号,经过2km的光纤传到控制室,在控制室内,又通过光模块与LVDS模块,将光信号转成电平信号直接给了FPGA模块与USB模块。

2 硬件设计

如图一所示,计算机与USB模块通过USB电缆连接,计算机发给USB模块读数命令、启动DS92LV1224工作命令及其他工作命令,USB模块将命令传给FPGA模块,再由FPGA来直接控制LVDS芯片的工作状态。由于本系统USB模块传给计算机的速度最快为140Mbps,可以将100Mbps速度的数据适时的传到计算机里。

3 延长距离设计。

(1)弹上延长距离设计:

LVDS信号的传输是依靠串行器和解串器成对出现相互搭配来完成的,串行器和解串器都需要外部给它们一个工作时钟。只有这两个工作时钟频率相等,串行器和解串器之间才能正常通信。由于FPGA管脚与内部逻辑的灵活性,完全可以解决时钟频率相等的问题。

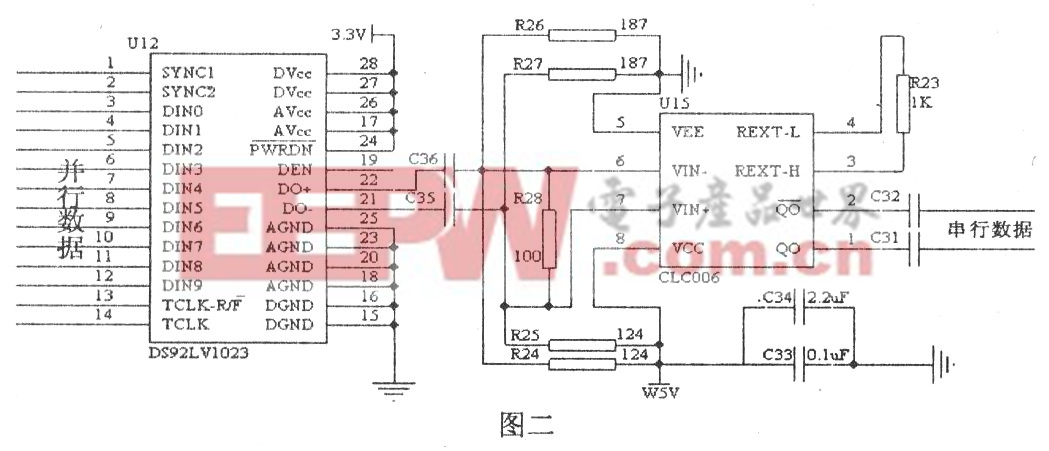

发送端:串行器DS92LV1023是将外部并行数据串化成串行数据,此时该串行器输出的差分压差是lOOmV左右,这种小压差只能传输不到十米的距离,但加上CLC006这款电缆驱动芯片后,其输出压差可达到2V(压差可通过电阻R23调节),这样就可以驱动同轴电缆传输300米的距离。其部分电路图如图二所示。

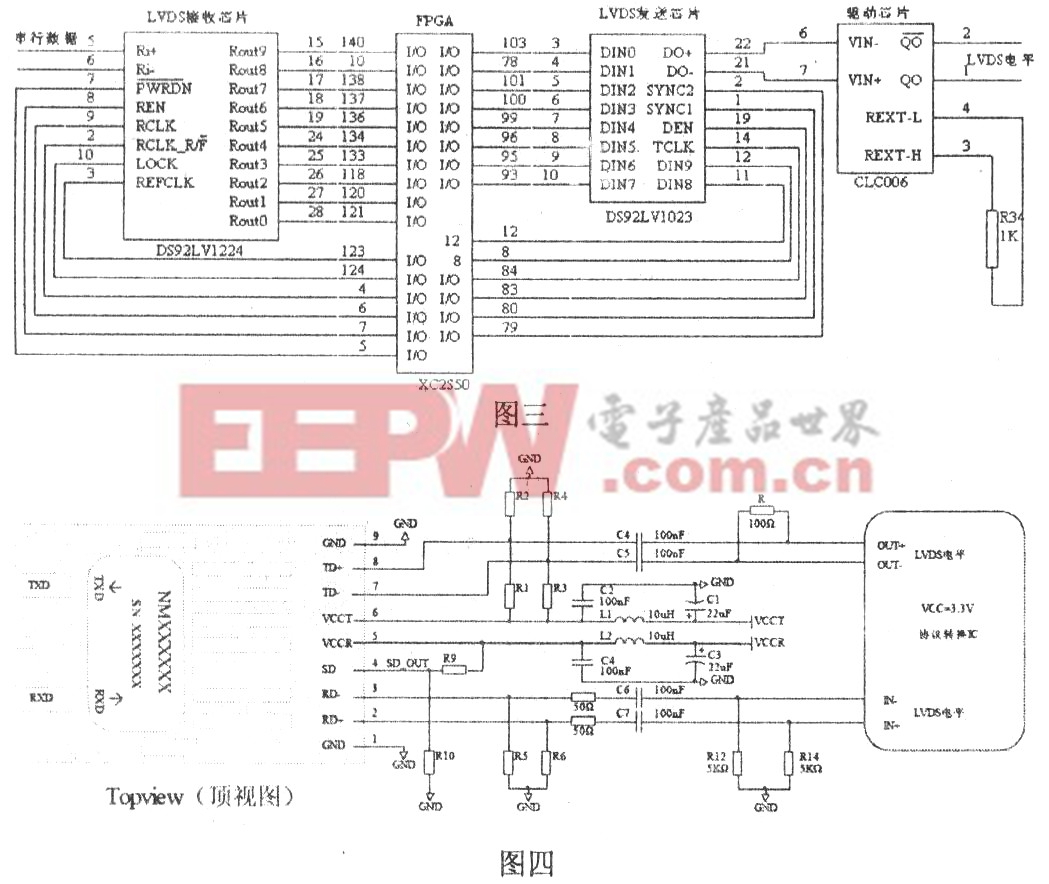

接收端:其部分电路如图三,解串器DS92LV1224解串出来的数据先经由FPGA模块再送给LVDS发送芯片,再经过驱动芯片CLC006之后信号变得很强,足以使光模块接收到此信号。

(2)地面上延长距离设计:

如下图四,将图三的LVDS电平直接接到下电路的光模块的发送端,经过反复试验,已经可以传输10km的距离。在光模块的接收端将光信号转成LVDS电平,再经过LVDS模块转化成数字信号,再做进一步处理。

4 速度匹配

由于LVDS所传输的信号是数据采集系统刚采集到的数据,这个数据的速度只有几百KByte/s,而这一款LVDS芯片传输速度范围是10一66MByte/s。可以采用间歇式传输,但是这种LVDS芯片在传输过程中进行中断后,再次传输需要500μs的同步时间,所以如果LVDS芯片进行间歇式传输时,会丢失掉500μs的数据,不能采用这种方式。

串行器DS92LV1023和解串器DS92LV1224的芯片有10个数据管脚,一般数据都是8位,其中有两位一般不用。在这里这两位空数据位就起到作用了:先将采集回来的数据暂存到FPGA中的内部Fifo里,等到Fif0中数据达到10个字节以上就通知FPGA模块将数据和时钟赋到串行器DS92LV1023的管脚上传输数据,同时通过FPGA给串行器DS92LV1023的第Data8位赋值为“0”;当传完采集回来的数据后,我们可以加一些我们自己产生的数据,使LVDS可以持续的传输下去,与此同时通过FPGA将串行器DS92LV1023的第Data8位赋值为“1”。

以上是数据源发送端速度配合的处理,下面再谈谈数据接收端到上传到计算机上的速度配合。

USB模块给计算机上传数据也是间歇式传输,也就是说USB模块每传512个字节,就要停顿几个μs。所以就在FPGA中做一个内部Fifo先将数据暂存到内部Fifo里,等到Fifo中数据达到512个字节以上就通知USB模块可以读数了,这样就将数据读回到计算机里。

通过FPGA控制解串器DS92LV1224PWRDN、REN、RCLK、RCLK_R/F、及REFCLK管脚使LVDS芯片开始解串,由于解串器DS92LV1224解串出来的数据分了两部分:一是采集的真正数据,二是我们自己加的数据。所以,要先把自己加的数据过滤掉,这个工作让FPGA来做就可以了,通过FPGA判断DS92LV1224的Data8位,如果Data8为“0”,则将数据存到FPGA的fifo里。

5 结论

本文介绍了一种基于LVDS总线与光纤结合的高速数据传输系统的设计方法,并对设计中整个数据流程、FPGA对LVDS芯片工作状态和FPGA与单片机的配合作了详细描述。本系统已经投入实际应用,其性能可靠、稳定,适用性强,该方法值得推广。

评论