数字继电保护系统中CAN总线通信的实现

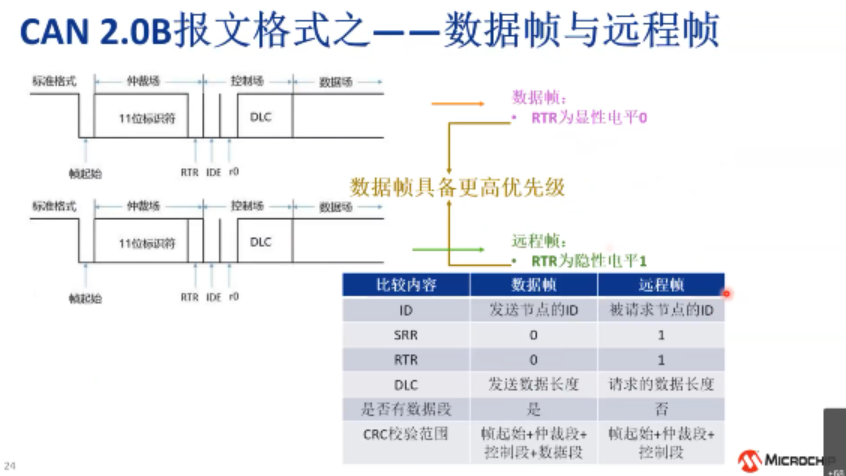

CAN总线是一种多主总线,即每个节点机均可成为主机,且节点机之间也可进行通信,总线上各个节点共享通信介质,因此必须解决各节点竞争使用总线而引起的冲突问题。CAN总线采用了一种独特的基于报文静态优先级的非破坏性带冲突检测的载波侦听多路访问(Nondestructive CSMA/CD)总线仲裁技术[3]。

报文的头部识别符定义一个静态的报文优先级。只要总线空闲,任何节点都可以开始发送报文。如果2个或2个以上的节点同时开始传送报文,此时就会出现总线访问冲突。通过识别符的按位仲裁可以解决这个冲突。仲裁期间,每一个发送器都对发送位的电平与被侦听的总线电平进行比较。如果电平相同,则这个节点可以继续发送;如果不同,退出发送。

CAN总线上电平用“显性”(逻辑“0”)和“隐性”(逻辑“1”)来表示,当同时出现“显性”和“隐性”时,其结果是总线电平呈“显性”。如果节点1发送的是“隐性”电平而节点2发送的是“显性”电平,两节点侦听到的总线电平则是“显性”,这样节点1就失去了仲裁,必须退出发送状态,而节点2赢得仲裁可以继续不受影响地发送报文。CAN总线这种非破坏性总线仲裁机制确保了报文和时间均不损失。

除了上述非破坏性总线仲裁机制的特点,CAN总线还具有如下显著的特点[4]:① CAN总线具有完善的错误处理机制,包括侦听、CRC校验、位填充技术、帧格式检查等以及一些相应的准则。CAN总线上,任何检测到错误的节点都会发出一串称为“错误标志”的位流,标记出已损坏的报文。此报文会失效并将自动地开始重新传送。 因此,它的可靠性很高。

② 数据段长度最多为8个字节,不会占用总线时间过长,从而保证了通信的实时性。如MCP2510 CAN控制器的串行速率为1M,最长报文发送时延为64µs(8×8/1=64)。但这同时也反映了其不适于传输长报文的局限性。

考虑到数字继电保护系统中的开关量信号,包括断路器位置状态信号、保护投入信号、分合闸与报警信号等,都是几个字节的小数据量信息,但是对实时性和可靠性要求很高,在保护系统中应用CAN总线传输开关量信号,可以充分发挥CAN总线的技术优势。

2 DSP的McBSP与CAN控制器接口的设计

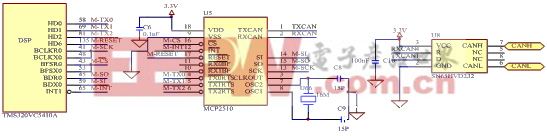

CAN总线通信模块由MICROCHIP公司的CAN总线控制器MCP2510[5]和TI公司CAN总线收发器SN65HVD232[6]组成,如图1所示。MCP2510是带SPI接口的CAN控制器,与CAN2.0A/B协议兼容,支持CAN1.2、CAN2.0A、CAN2.0B的被动/主动版本协议,实现CAN总线的逻辑链路控制和介质访问控制,能够发送、接收标准和扩展报文,位速率可达1Mbps,它还具有验收过滤和消息管理的功能,包括3个发送缓冲器和2个接收缓冲器,减少了微控制器(MCU)管理的负担。SN65HVD232是CAN协议控制器和物理总线的驱动接口,为总线提供不同的发送能力和对CAN控制器提供不同的接收能力,与ISO11898标准兼容。

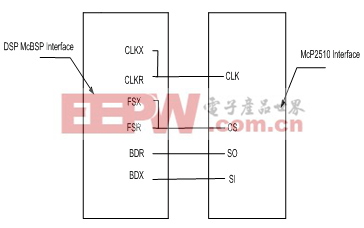

本文选用TI公司高性能C54系列的DSP作为控制核心,型号为TMS320VC5410A,工作主频160MHz。TMS320VC5410A提供高速、双向、多通道带缓冲串行接口McBSP与MCP2510的SPI(工业标准串行外围接口)接口,两者连接关系如图2所示。

McBSP功能强大,结构复杂,要实现二者的通信,关键要对McBSP的各寄存器进行合理配置,包括主从方式选择,时钟信号、帧同步信号的产生,数据收发的沿边选择,时序配合等,下面分别加以论述。

时钟与帧同步信号的连接关系表明McBSP工作在主(Master)方式,MCP2510 工作在从(Slave)方式。McBSP的发送时钟由DSP内部采样率发生器产生(发送时钟模式位CLKXM=1),采样率发生器时钟由DSP内部时钟产生(采样率发生器时钟模式位CLKSM=1),McBSP的接收时钟由发送时钟驱动(接收时钟模式位CLKRM=0),MCP2510的时钟由McBSP给出,总之,所有的时钟源头是DSP的内部时钟;同时,发送帧同步信号FSX由McBSP内部寄存器DXR向XSR的数据拷贝动作产生(发送帧同步模式位FSXM=1,采样率发生器发送帧同步模式位FSGM=0),接收帧同步信号由发送帧同步信号驱动(接收帧同步模式位FSRM=0)。

根据如图3所示的内部连接图中时钟和同步信号流程分析,McBSP内部时钟信号(Internal CLKX、Internal CLKR)、帧同步信号(Internal FSX、Internal FSR)与MCP2510的时钟信号、片选信号同步产生与停止。McBSP内部发送帧同步信号Internal FSX是从低电平跳到高电平,而与之相连的MCP2510片选信号是高电平跳到低电平有效,相位相反,故McBSP内部寄存器的发送帧同步信号极性位FSXP=1,而McBSP内部帧同步信号Internal FSR与Internal FSX必须一致,故Internal FSR也必须和MCP2510片选信号反相,接收帧同步信号极性位FSRP=1。

评论