TMS320F2812与ARINC429数据总线之间的通信设计

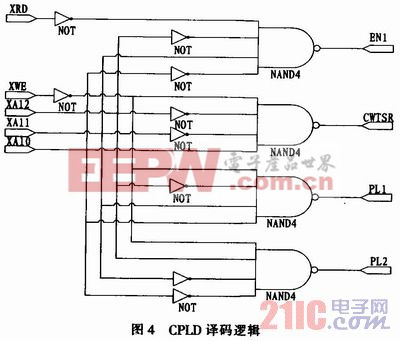

CPLD集成了系统地址选择模块,实现对外部器件的访问。CPLD的逻辑功能决定了HS-3282的功能地址,通过地址译码产生HS-3282所需要的控制信号PL1、PL2、EN1和CWSTR所需要的控制信号。系统中译码模块的逻辑如图4所示。由片选使能和CPLD译码逻辑可得PL1、PL2、EN1和CWSTR的选通地址。本文引用地址:http://www.eepw.com.cn/article/156580.htm

3 系统软件设计

此系统的软件部分主要包括初始化模块、数据的发送/接收子程序模块。

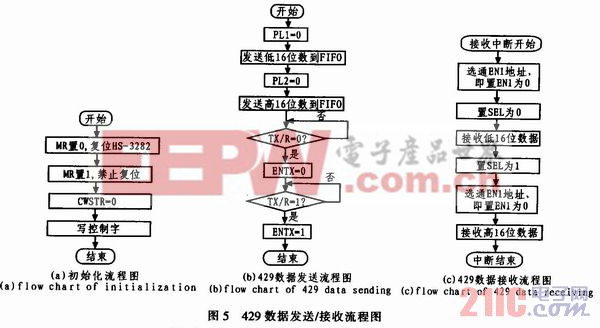

1)初始化模块系统上电后,首先进行初始化,初始化模块包括上电芯片复位和写控制字到HS-3282控制字寄存器。该控制字主要有字长、接收速率、发送速率、源目的解码和自测试设置。初始化流程图如图5(a)所示。

2)ARINC429数据发送模块数据发送是首先向FIFO写入数据,然后经HS-3182驱动发送到总线。在向FIFO写操作过程中,PL1先于PL2有效,多次的写PL1将会使先前的数据被覆盖,PL1有效时,低16位数据被发送到FIFO中。当PL2有效时,高16位数据被传送到FIFO中。第1个数据字写入后TX/R由高变低,然后通过置发送使能信号ENTX,HS-3282将数据字串行发送出去,并自动在相邻两个字之间插入4bit间隔。当FIFO为空时,TX/R由低变高,此时应当禁止发送使能信号ENTX,以便向FIFO重新写入数据。当HS-3282处于发送状态时,不能向FIFO写入数据。发送模块流程图如图5(b)所示。

3)ARINC429数据接收模块 数据接收模块被设计为中断接收,由HS-3282的D/R1提供中断信号。当D/R1为0时,进入中断,并表明ARIN-C429总线上有数据到来,此时选通EN1地址,再置SEL为0,接收低16位数据;接着置SEL为1,再选通EN1地址,接收高16位数据。接收模块流程图如图5(c)所示。

4 结束语

针对ARINC429总线的应用,提出了TMS320F2812与ARINC429总线通信的软硬件设计和实现方案。该设计硬件电路简单,数据通信程序可读性好,编写容易,数据传输准确可靠。在设计TMS320F2812数据总线读写的逻辑控制时,XRD和XWE信号必须参与逻辑控制,保证顺利读写总线数据。经验证该系统能够有效地完成2个16位并行数据到32位串行数据的转换,实现了TMS320F2812 DSP与ARINC429总线之间的数据通信,且传输速率为100 kb,达到了系统的设计要求。该系统可广泛借鉴并应用于ARINC429总线数据传输系统及ARINC429接口卡设计中。

评论