基于IXP2400的安全网关实现研究

摘要: 讨论了在IXP2400上应用IPSec实现安全网关的一种方案,可为通过的业务流提供较强的安全性。

关键词: 网络处理器; IXP2400; 微引擎; IPSec

IPSec是一种基于IP层的通信安全机制,是目前唯一一种可为任何形式的通信提供安全保障的协议,因而实现具有IPSec功能的网关能保证IP层通信的安全。然而,用IPSec对数据包进行认证、加/解密处理等,都是比较耗费资源的工作,容易使具有IPSec功能的网关设备出现瓶颈问题;同时,基于ASIC研发具有这类复杂功能的新产品更为困难。因此,传统的网络解决方案已在处理速度和灵活性两方面受到挑战。具有通用CPU的灵活性和ASIC芯片的执行速度的可编程网络处理器的出现,为IPSec机制在线速网关设备的应用提供了新途径。

本文介绍了Intel的IXP2400网络处理器的特点、结构以及IPSec体系结构,讨论了在IXP2400中以IPSec实现安全网关的一种方案。

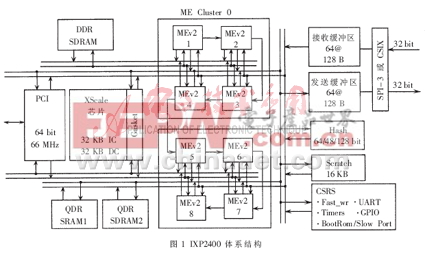

1 IXP2400的体系结构

网络处理器(Network Processor)是一种面向包结构处理的专用器件。IXP2400是Intel公司第二代高性能网络处理器之一,是在第一代网络处理器的基础上,实现了高性能的并行处理结构,从而能够实现复杂的算法、深入查看包内容、进行流量管理及以线速(2.4 Gb/s)转发包等;并首次采用Intel的超任务流水线技术,允许将1个包处理任务分解为多个易于衔接的、有序的子任务,并确保微引擎间通信的低时延。在体系结构上,具有以下特点:

(1)多处理单元结构,各单元独立运行,并以硬件实现多线程技术,线程间无任何需切换开销。

(2)以软件流水线的形式分派任务到各处理单元,各处理单元可并行操作。

(3)ALU采用优化过的指令,专用于数据包处理,1条指令能在1个时钟周期内完成。

(4)具有一些完成特殊功能的硬件单元,如CRC校验、Hash计算、甚至加/解密运算单元,用于加速专用处理。

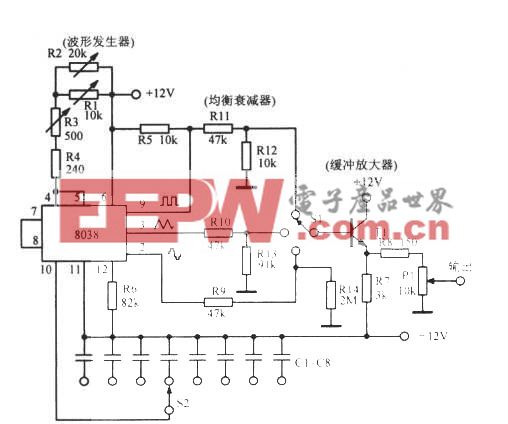

IXP2400的体系结构如图1所示。

其主要功能部件如下[1]:

(1)XScale:32位的RISC高性能通用处理器,用于初始化、管理整个芯片,同时能执行高层网络处理任务,如复杂的算法处理、路由表维护等。

(2)Microengine(MEv2):8个相互独立的32 bit可编程微引擎,是处理数据的主要场所,各微引擎间用寄存器通信。每个微引擎主要包括:1个存放该微引擎运行程序的控制存储器、8个硬件支持的线程、数据通路和控制状态寄存器、1个ALU及1个CRC单元等。

(3)存储器控制器:用于控制访问片外RAM,包括SRAM、DRAM。SRAM主要用于存储各种控制信息,如路由表等;DRAM主要用作数据处理的缓冲区。

(4)Scratch:片内的16 KB通用存储器,存放各种经常需快速查找的数据。

(5)Hash:能对48 bit、64 bit或128 bit的数据作Hash运算,并生成索引。

此外,IXP2400中还采用了一些如硬件队列等技术来提高ALU的处理速度。

2 IPSec的工作原理

IPSec的安全服务是通过在IP层对所有数据流使用密码和安全协议联合实现的,能保证应用程序通信的安全性。它能应用于防火墙和路由器等网关设备,对上层应用是透明的。

IPSec利用2种通信安全协议[2]:认证头(AH)和封装安全载荷(ESP)。还有用于密钥交换和管理的Internet密钥交换协议(IKE)[2]和相应的认证/加密算法等协议组件。AH和ESP既可用于保护一个完整的IP包,也可以用来保护IP包中的上层数据。此外,还可以组合使用,实现不同的安全保护级别。AH和ESP使用2种工作模式[3]:传输模式和隧道模式。

由于IPSec体系设计与算法无关,因而可以为不同的通信对等体选择不同的安全算法。为维护这些动态存在的安全策略,在实现IPSec时,需要定义相应的安全策略数据库(SPD),其中的每1条记录就是1条安全策略。

为正确处理具有IPSec功能的IP包,IPSec通信对等体需要将经协商一致后所采用的安全协议、工作模式、加密/认证算法、密钥等信息与所建立的链路结合起来,才能为不同的数据流提供不同的安全保护。其实现方法就是在IPSec通信对等体间建立安全关联(SA)。SA是通信对等体之间为进行安全通信而协商的一种约定。SA可由1个三元组唯一标识,表示为安全参数索引(SPI),目的IP,安全协议标识>。

为维护所有活动的SA参数,在实现IPSec时,需要定义相应的SA数据库(SAD)。IKE的主要功能就是在IPSec通信对等体间动态进行通信参数协商[4],并提供经认证的密钥信息,从而建立起SA,对其进行维护和管理。

3 IPSec在IXP2400中的实现

3.1 程序设计

网络应用程序中,网络信息的处理通常包含在以下2个逻辑层面中[5]:

(1)数据层面:负责高速处理、转发数据包。因所有要处理的数据包都必须通过该层面,故其性能直接影响到整个程序的性能。

(2)控制层面:主要处理协议信息,并负责创建、配置及更新各种表和数据集,供数据层面查找使用。如处理含路由信息的RIP、OSPF包,然后更新IPv4转发表,供数据层面使用。

网络处理器就是完成这2个层面的功能。

在IXP2400中,将数据层面分为快速通道和慢速通道。快速通道主要由各微引擎构成,完成绝大多数包的正常处理,如IP包转发等;慢速通道主要由XScale构成,处理少数需复杂处理的包,如异常包、包分段等。考虑到处理速度的要求,在快速通道中通常将处理任务以软件流水线形式分配到多个微引擎中实现,每个微引擎以编程方式实现所指定的任务。当一个微引擎完成其任务后,将包传到下一微引擎继续处理,直至完成整个任务。每个微引擎的流水线又可由若干流水线级构成,这些流水线级是顺序执行的。由于每个微引擎有8个线程并发(甚至有数个微引擎的线程在并行)执行相同任务,因而要按序正确处理数据包,就必须考虑各线程访问临界区代码的同步问题。为保证指令尽可能少,以达到线速要求,一种处理方法就是:在一个微引擎中让各线程顺序执行,并且每个线程顺序执行所有流水线级。如某个流水线级的功能对所处理的包并不要求,则在执行到该流水线级时必须进入等待,当线程下一次获得运行时再执行下一流水线级;如有数个微引擎在并行执行同一任务,则必须考虑微引擎间的执行顺序。可见,将少数包要求的复杂处理任务交给XScale,能有效减少微引擎不必要的等待时间,加快数据的处理速度。

对于控制层面,因所要处理信息复杂、广泛,涉及的指令范围广,数据层面中的快速通道是难以处理的,因而应放在XScale中实现[5]。

通常,将快速通道处理任务按逻辑划分为若干功能块,在可编程的微引擎中,每一块实现称为一个微功能块(microblock)。而将运行在XScale中的微功能块对应的慢速通道处理部分称为核心组件(Core Component),完成相应微功能块的配置、初试化及维护共享数据结构,并处理微功能块发送的异常包或信息。此外,各种路由协议也运行在XScale中,处理各种协议信息。这样实现了数据层面和控制层面的分离,两层面间可用标准API通信。

将所有任务放在一个IXP2400中实现,可能满足不了线速要求,因而通常将任务分配到2个IXP2400来实现。这样对于需要较多指令的微功能块,可指定多个微引擎并行运行,适当增加每个微引擎的执行时间。

3.2 系统功能

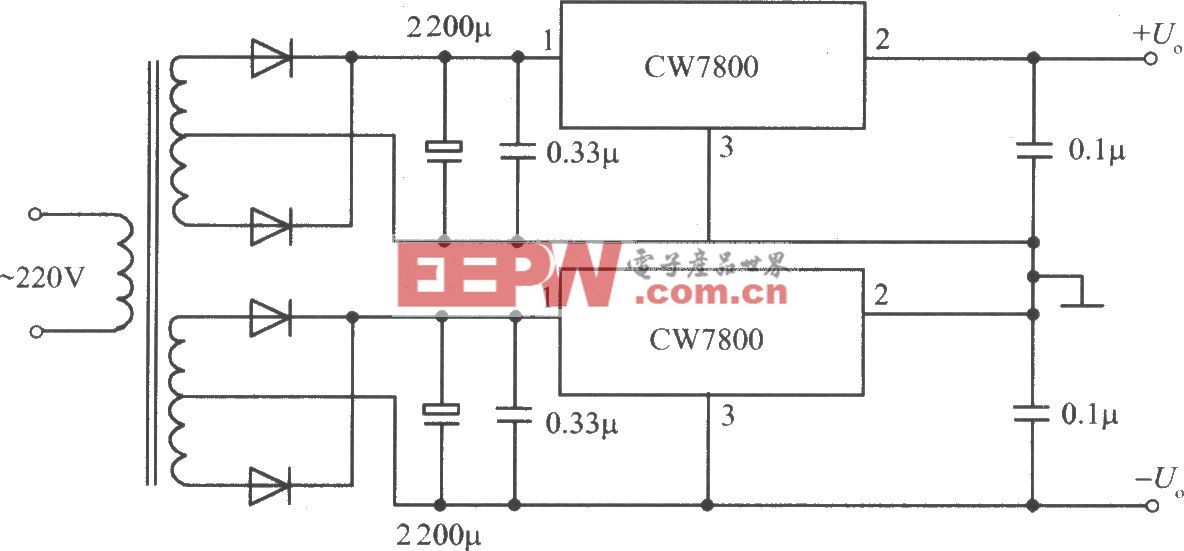

综上述分析,实现方案的系统框图如图2所示。

评论