基于千兆以太网的高速数据传输系统设计

2.3 系统实现

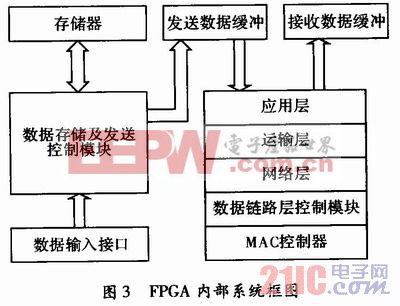

千兆以太网由物理层、数据链路层、网络层、运输层和应用层组成。在FPGA内部实现MAC层以及MAC层以上的部分TCP/IP协议,其中包括ARP协议,IP协议,UDP协议以及部分ICMP协议。物理层使用DP83865芯片。FPGA内部系统框图如图3所示。本文引用地址:http://www.eepw.com.cn/article/156459.htm

MAC控制器上层的协议在FPGA内部用硬件描述语言实现,这些协议将与MAC核共同组成网络控制系统,各部分协议之间密切配合,共同完成网络数据收发的功能。协议系统的时钟速率设定为125 MHz,可以最大程度地发挥MAC核的作用,使千兆以太网的数据吞吐率达到最大。

系统中关键的技术问题在于协议的效率问题。在调试初期,先以百兆速度运行,由于系统时钟为25 MHz,相对较低,没有出现程序因效率低下而导致系统不稳定的情况。当在原有基础上改为千兆以太网时,系统出现不稳定地情况,所发送的数据帧不能稳定地发送至上位机,有丢失数据帧的情况。

于是对协议部分进行优化,以提高其运行效率。在编写程序时,良好的代码风格尤为重要。时序电路中最重要的是状态机,所以状态机的性能在一定程度上决定了整个程序的性能。协议中状态转移比较复杂,对状态进行合并、减少状态数量之后,程序效率明显提高。此外,由于需要处理大批量的数据,而且数据将流经每一层协议,因而各层协议之间使用完全流水结构,衔接紧密,实时性更高,而且不必为每一

层开辟缓冲区,节省了资源。

2.4 上位机控制

使用Visual C++编写上位机程序,上位机通过网络向FPGA发送相关命令,FPGA接收到命令后进行相应操作,并将数据通过千兆以太网发送至计算机,由上位机程序对接收到的数据进行存储。上位机程序在MFC环境下使用WinSock编程实现,使用面向无连接的数据报套接字,即采用UDP协议,无需建立连接。为提高系统效率,在程序中使用多线程技术,一个线程负责接收数据,一个线程负责存储数据,可以有效提高程序运行效率。

2.5 测试结果

在系统中,将存储在电路板上Flash中的数据通过千兆以太网传输至计算机,使用UDP协议,每次传输1 024 Byte。经测试,此千兆以太网性能稳定,数据吞吐率高。图4所示是由SignalTap II采样得到的由FPGA输出的UDP波形,采样时钟为250 MHz。

在图4中,rx_clk为125 MHz时钟,gm_tx_d是由MAC发送至物理层芯片的数据帧。由图可见,MAC软核每个时钟周期发送8 bit数据,则此千兆以太网带宽为1 000 Mb·s-1。千兆以太网额外开销小,大约占用FPGA资源的7%,为系统留下了充足的设计空间。对千兆以太网进行测试时,每次发送数十万数据帧至上位机,当检测到错误帧或数据帧丢失时立即停止发送,在所进行的一系列测试中,没有出现中途停止发送的情况,说明没有数据帧丢失或在传输中出错,系统工作稳定。

数据传输至计算机后由上位机程序接收并存储,由于上位机程序效率偏低,千兆以太网传输速率受到限制。如果进一步优化上位机程序,可以提高千兆以太网带宽利用率。若两个电路系统使用千兆以太网互连,因为都是纯硬件电路,运行效率较高,可以发挥千兆以太网高带宽的特性。

3 结束语

设计中使用三速以太网软核,并对源程序进行了一系列优化,代码效率较高,系统工作稳定,资源利用率较高,数据吞吐率最高可达1 000 Mb·s-1。千兆以太网成本低,可以在多种平台下应用,为高速数据传输提供了方便的途径。

tcp/ip相关文章:tcp/ip是什么

评论