基于DDS跳频信号源的设计与实现

摘要:数字频率合成(DDS)结构简单、易于控制,产生的跳频信号具有很高的频率分辨率和频率转换速度。文章通过对DDS原理的分析,在FPGA平台下对基于DDS的跳频信号源进行设计,并通过优化参数设置,进一步提高跳频信号源的整体性能。

关键词:跳频信号:数字频率合成;现场可编程门阵列

0 引言

跳频通信具有较强的抗干扰、抗多径衰落、抗截获等能力,已广泛应用于军事、交通、商业等各个领域。频率合成器是跳频系统的心脏,直接影响到跳频信号的稳定性和产生频率的准确度。目前频率合成主要有三种方法:直接模拟合成法、锁相环合成法和直接数字合成法(DDS)。直接模拟合成法利用倍频(乘法)、分频(除法)、混频(加法与减法)及滤波,从单一或几个参考频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗高,目前已基本不用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简单、便于集成,且频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。DDS是近年来迅速发展起来的一种新的频率合成方法。这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,非常适合跳频通信的要求。

1 DDS的基本原理

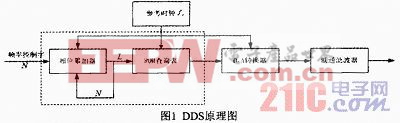

DDS的原理如图1所示,包含相位累加器、波形存储器(ROM)、数模转换器(DAC)和低通滤波器4个部分。在参考时钟的驱动下,相位累加器对频率控制字N位进行累加,得到的相位码L作为ROM的地址,根据地址ROM输出相应幅度的波形码,然后经过DAC生成阶梯波形,经低通滤波器后得到所需要的连续波形。

理想单频信号可以表示为Y(t)=Usin(2πf0+θ0)。如果振幅U和初始相位θ0为一个常量,即不随时间变化,则输出频率由相位唯一确定f0=θ(t)/2πt。

以采样频率fc(Tc=1/fc)对单频信号进行抽样,则可得到相应的离散相位序列

![]()

其中△θ·n=2πf0/fc是连续两次采样之间的相位增量,控制△θ可以控制合成信号的频率。把整个周期的相位2π分割成q等份,每一份δ=2π/q为可选择的最小相位增量,得到最低频率输出fmin=δ/2πTc=fc/q,经过滤波后得到S(t)=cos(2πfct/q)。

如果每次相位的增量选择为δ的R倍,即可得到信号频率f0=Rδ/2πTc=Rfc/q,相应得到的模拟信号为S(t)=cos(2πfcR/q)。

由以上原理可知,DDS输出信号的频率与参考时钟频率及控制字之间的关系为f0=K·fc/2N,式中f0为DDS输出信号的频率,K为频率控制字,fc为参考时钟频率,N为相位累加器的位数。在波形存储器中写入2N个正弦波数据,每个数据有D位。不同的频率控制字导致相位累加器的不同相位增量,从而使波形存储器输出的正弦波的频率不同。

2 基于DDS的跳频信号产生核心模块的设计

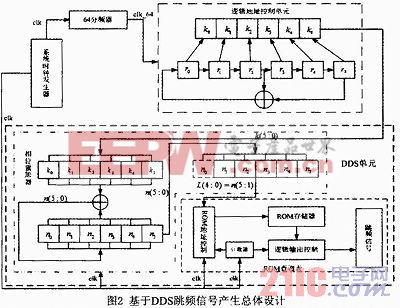

图2为基于DDS跳频信号产生的总体设计。

如图2所示,整个系统由两个部分组成,即逻辑地址控制单元和DDS单元。其中DDS单元又包括相位累加器和ROM查询表。逻辑地址控制单元用来产生不同的频率控制字,改变相位累加器的累加值。DDS单元依据频率控制字产生相应频率的信号。

评论