基于Lab Windows/CVI的PC与 DSP的串行通信

2.3 下位机DSP程序

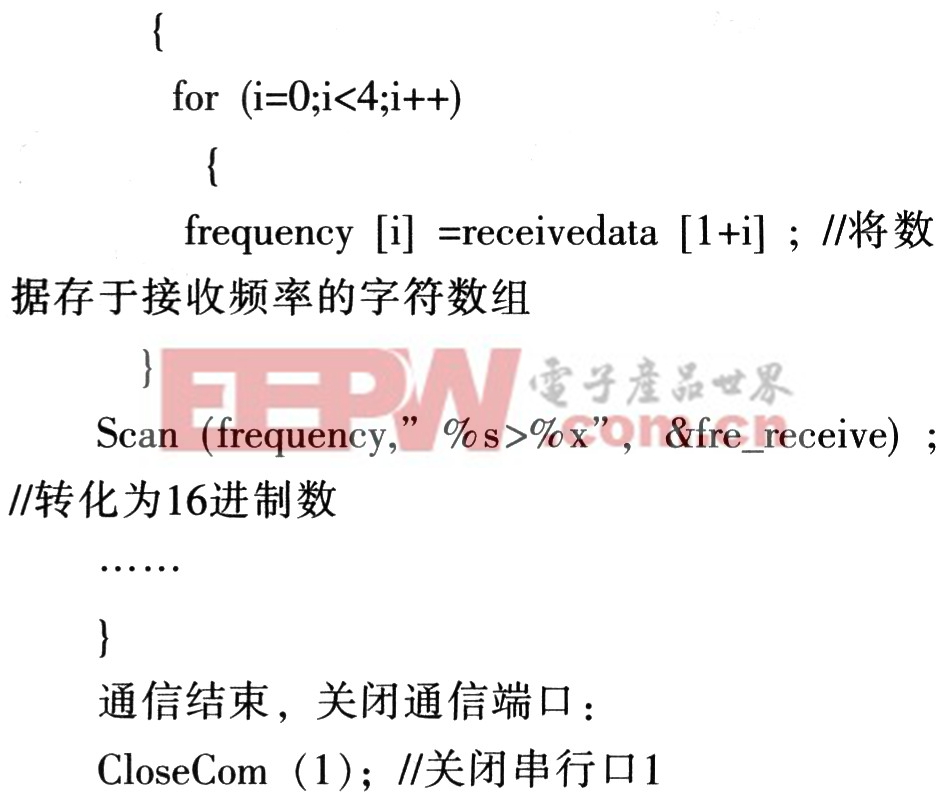

DSP的软件开发可利用集成开发环境CCS3.1(Code Composer Studio),并采用C语言进行编程。利用DSP的SCI模块实现串行通信的主程序流程图如图4所示。DSP的串行通信程序设计可采用查询法或中断法来进行数据的收发,这里采用中断方式接收数据,而用查询方式发送数据。DSP收到PC机发送来的数据时,便转入相应的中断子程序,其中断服务子程序流程如图5所示。其串口SCI初始化配置如下:

void SCI_Init(void)

{

SciaRegs.SCICCR.all=0x0007;//字符长度8位

SciaRegs.SCICTL1.all=0x0003;//使能发送和接收

SciaRegs.SCICTL2.all=0x0002; //使能接收中断,禁止发送中断

SciaRegs.SCIHBAUD=0x00;//置波特率高8位

SciaRegs.SCIHBAUD=0xF3;//置波特率低8位

SciaRegs.SCICTL1.all=0x23;//使SCI退出复位

}

DSP收到字符串”~010105F0019D”之后,首先进行和校验。如果正确,则根据功能码和参数码判断PC机发送的是否是修改参数P的命令。然后提取数据”05F0'’,将其转换为十进制数1520,再除以100即得到要设置的P值15.20;如果和校验出错,则要求主机重发。若PC机发送的是上传数据的命令,则将发送标志变量send_flag置1,这样,在主循环中,经过判断后,便可向PC机发送数据。

3 结束语

本文利用LabWindows/CVI开发平台编写了上位机PC程序,同时利用CCS3.1开发环境编写下位机DSP程序,然后通过RS232总线进行串行通信。利用这种方法设计的PC机与DSP的串行通信系统具有硬件结构简单、成本低、实现容易等特点,并具有良好的可移植性和可扩展性,能够很好地满足PC与DSP的通信需求。

评论