基于ATmega128的无线数据采集系统

1 设计思想

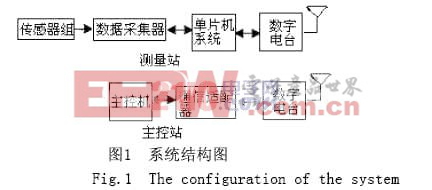

数据采集单元采用先进的ATmega128嵌入式单片机作为核心部件,利用RS-485通信接口与控制系统通信。测量站主要是将捕捉的现场信号经转换器ADC采样、量化、编码后,变成数字信号传给微处理器,接收遥控指令并发送数据;主控站的主要工作是发送遥控指令、接收数据信息、进行数据处理和数据管理。整个系统结构简单,可靠性高。见图1。

1.1 高速的模数转换芯片TLC5510

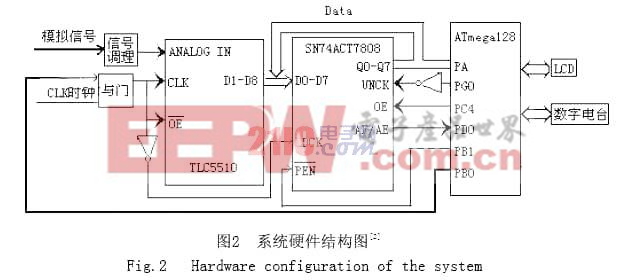

该系统的A/D转换采用TLC5510模数转换芯片。TLC5510模数转换芯片是TI公司的8位A/D转换器,是一款高速、低功耗且内部带有采样保持电路。它的数据采集时序是当CLK为高电平时转换数据,当CLK为低电平时输出有效数据。当要从A/D中读取数据时,只要 保持低电平即可,当

保持低电平即可,当  为高电平时D1-D8为高阻态.见图2.

为高电平时D1-D8为高阻态.见图2.

1.2 数据采集系统的接口电路设计与流程

FIFO芯片SN74ACT7808是2048字节×9位可以实现先进先出异步读写操作的双端口存储器.读写操作会自动访问存储器中连续的存储单元。从FIFO中读出的数据顺序与写入的顺序相同,地址的顺序在内部已经预先定义好了。对FIFO的读写操作只由读写信号控制,不需要另外的地址信息。这使得FIFO的控制电路变得十分简单:读数据时只要OE保持为高电平同时使UNCK产生一个上升沿;写数据只要LDCK产生一个上升沿即可.

由于是高速数据采集,单片机相对A/D来说速度远远不够,所以需要设计一个电路让数据采集与存储自动完成,见图2。单片机的PB0引脚通过与门与外部CLK时钟相连,这样单片机就可以控制A/D的采样。当PB0为高电平时进行采样,当PB0引脚为低电平时A/D的CLK没有脉冲,采样停止。当FIFO保存的数据几乎满后给单片机一个中断信号,单片机接到中断信号后置PB0为低电平停止采样,然后把数据从FIFO中读出。因为单片机的PG0引脚经反向器后接到FIFO的UNCK,PC4脚接到FIFO的OE,它的有效地址只要保持PC4引脚为高电平即可。数据处理完毕后再接着采样,如此反复,完成周期性采样[2]。

2嵌入式单片机ATmega128与数传电台的串行通信

ATmega128为基于AVR RISC结构的8位低功耗CMOS微处理器。ATmega128的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。8通道10位ADC(具有可选的可编程增益)、具有片内振荡器的可编程看门狗定时器、SPI串行端口、异步串行口与JTAG测试接口(此接口同时还可以用于片上调试),以及六种可以通过软件选择的省电模式。

2.1 ATmega128的串行通信方式

串行通信波特率:9600bps,发送接收方式:一位起始位,8位数据位,奇校验,1位停止位。UARTO初始化可以在ICC AVR中设置完成,而且Builder自动生成中断服务子程序和人口地址,只需在服务子程序中加人处理代码即可。

//UARTO initialisation

//desired baud rate:9600

//char size:8bit

//parity: Disabled

void uart0_init(void)

{

UCSR0A=0x00;

UCSR0B=0x98; //接收完成中断允许,发送数据允许.

UCSR0C=0x06; //发送接收的字符长度为8位.

UBRR0H=0x00;

}

接收数据时,单片机设置一个标志,假设接收到第一个“*”字符,标志置1,认为通信正常,可以接收数据。接收数据时,判断是否收到接收完成消息;是,则清除标志,使得下次收到的数据无效,直到再次收到“*”,标志置1。标志为1时,判断是否收到消息(字符值等于8);是,将上次收到字符清为0;不是则将接收到的数据保存到接收缓冲区中。执行操作后,最后将接收到的字符发回给计算机。单片机通信流程图见图3。

评论