标准单元ASIC和FPGA的权衡及结构化ASIC

图4 掩膜集成本的增加,既反映了深亚微米工艺的每个掩膜的复杂程度逐渐增加,又反映了要求用深亚微米工艺制造芯片的掩膜制造商数量不断增加(由Lightspeed Semiconductor公司提供)。

现在正在吹捧结构化ASIC器件的公司中有AMI Semiconductor公司, Chip Express公司, Faraday Technology公司, Fujitsu公司, Lightspeed Semiconductor公司, NEC公司, 和ViASIC公司。在这些公司中,目前只有AMI公司目前没有把自己定位为范围广泛的硅片供应商;该公司正在坚持向FPGA转换的有利地位,但是使用的是一种结构化ASIC基础,而不是过去的门阵列平台。相反,Lightspeed Semiconductor公司曾短暂扩入Xilinx FPGA降价市场,现已退出这一市场,将精力集中在传统的ASIC上(参考文献2)。Chip Express 公司的结构化ASIC采用各种备选方案中最细颗粒的逻辑模块;该公司估计其器件的每个逻辑模块将包含三到四个门电路,视具体设计而定。其他供应商的大多数逻辑模块能实现20~40个门的设计(图5)。

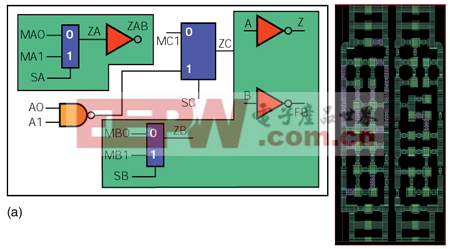

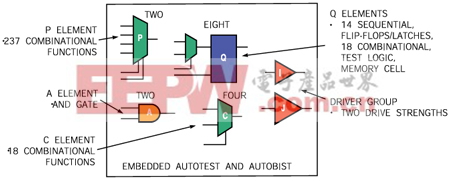

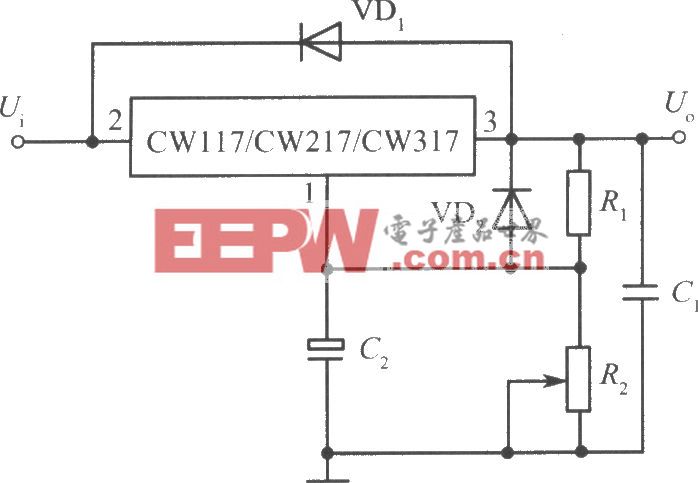

图5 结构化ASIC逻辑单元横跨从细颗粒(a)到粗颗粒( b )两种极端工艺方法(由Chip Express 公司和 Lightspeed Semiconductor公司提供)。

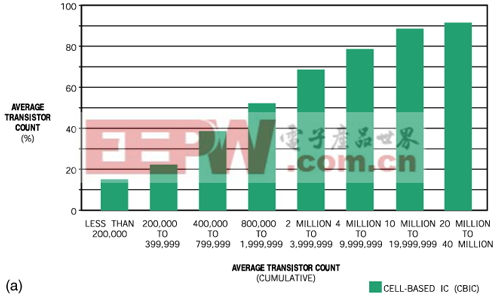

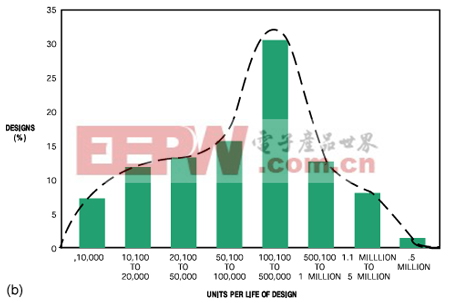

结构化ASIC供应商用各种混合的工艺制造芯。这种多样性反映了每个厂商都试图想在潜在的用户大蛋糕上占有自己单独的一份。供应商及其代工工厂摊消了他们用来开发后沿的易于理解的成品率高的0.18-微米、 0.25-微米、和0.35-微米工艺的生产设施与设备费用。您能用这些工艺实现的设计规模有个上限,但是相关的供应商指出:分析报告显示具有1百万门以下的ASIc设计占很大的百分比,同时有数据显示用户使用的ASIC设计,其中不足100000件批量的占50%(图6)。

图6 具有少量到中等数量的晶体管和门电路的设计覆盖了大多数ASIC市场(a), 大多数用户也以中小批量使用ASIC(b)( 由Xilinx 公司和 Leopard Logic 公司提供)。

在工艺技术另一端的是Fujitsu、NEC等公司。Fujitsu 公司现已将0.11微米结构化ASIC工艺投产,0.09微米工艺也将于2004年投产。NEC公司预示他们的90纳米工艺也将在2004年下半年投产。使工艺适合于设计是一种微妙的平衡行为,也涉及到了解设计的I/O缓冲器数量;供应商和用户希望发生的最后的事情是裸芯片在对最小尺寸起限制作用的I/O环路

内包含未被使用、从而浪费硅资源的区域。复杂封装的成本逐渐增加也使得封装内各种硅片的成本成比例地不相关。

结构化ASIC供应商声称从设计完成到第一个样品供使用的标准单元周转时间要从几个月缩短到几个星期。这种延迟不是从布局布线网表到FPGA提供的硅资源的几秒钟到几分钟的迟后时间,但是ASIC拥护者声称这种比较在某种意义上是苹果和桔子的比较。他们指出,随着FPGA和其内部的设计越来越复杂,工程师们为了实现区域(这个区域适合吗)和时间(它运行的足够快吗)收敛所花费的时间是指数增加的。工程师们认为,由于ASIC具有比FPGA更快的设计基础,所以花在模拟和重新设计方面的时间比较少,用结构化ASIC进行开发的总周期可能也因此而比用FPGA的更短。

硬件可定制的ASSP

结构化ASIC供应商用来使性能要求严格的电路的速度最大并实现诸如降低功耗、减小面积等其它功效的方法,就是将这些电路变成芯片的扩展部分而不是一般逻辑结构。例如Fujitsu公司声称其扩展的嵌入式触发器要比代替的方法能降低功耗50%,提高门使用率1.5~2倍。

Lightspeed公司将AutoTest 和AutoBIST快速测试电路嵌入模块化阵列ASIC中,以确保100%的固定型故障检测范围,并发现深亚微米造成的延迟故障。本文提到的每一个结构化ASIC供应商都提供扩展的嵌入式SRAM模块,而且如果您的设计需要的话,其中有些SRAM模块集成有时钟电路、高速串行和并行I/O缓冲器和其它具有丰富模拟功能的、对面积、电源和性能有严格要求的结构。

评论