基于16位8通道DASAD7606的系统布局考虑

在电力线路测量和保护系统中,需要对多相输配电网络的大量电流和电压通道进行同步采样。这些应用中,通道数量从6个到64个以上不等。AD76068通道数据采集系统(DAS)集成16位双极性同步采样SAR ADC和片内过压保护功能,可大大简化信号调理电路,并减少器件数量、电路板面积和测量保护板的成本。高集成度使得每个AD7606只需9个低值陶瓷去耦电容就能工作。

本文引用地址:https://www.eepw.com.cn/article/151138.htm在测量和保护系统中,为了保持多相电力线网络的电流和电压通道之间的相位信息,必须具备同步采样能力。AD7606具有宽动态范围,是捕获欠压/欠流和过压/过流状况的理想器件。输入电压范围可以通过引脚编程设置为±5 V或±10 V。

此电路笔记详细介绍针对采用多个AD7606器件应用而推荐的印刷电路板(PCB)布局。该布局在通道间匹配和器件间匹配方面进行了优化,有助于简化高通道数系统的校准程序。当通道间匹配非常重要时,此电路可以使用2.5 V内部基准电压源AD7606;而对于要求出色绝对精度的高通道数应用,此电路可以使用外部精密基准电压源ADR421,它具有高精度(B级:最大值±1 mV)、低漂移(B级:最大值3 ppm/°C)、低噪声(典型值1.75 μV p-p,0.1 Hz至10 Hz)等特性。低噪声及出色的稳定性和精度特性使得ADR421非常适合高精度转换应用。这两个器件相结合,能够实现业界前所未有的集成度、通道密度和精度。

电路描述

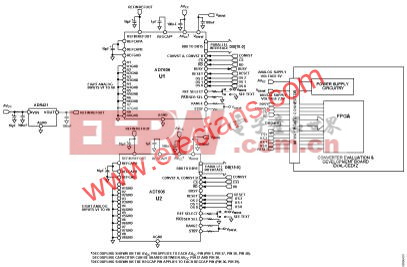

AD7606是一款集成式8通道数据采集系统,片内集成输入放大器、过压保护电路、二阶模拟抗混叠滤波器、模拟多路复用器、16位200 kSPS SAR ADC和一个数字滤波器。图1所示电路包括两个AD7606器件,可以配置为使用2.5 V内部基准电压源或2.5 V外部基准电压源ADR421。如果REF SELECT引脚接逻辑高电平,则选择内部基准电压源。如果REF SELECT引脚接逻辑低电平,则选择外部基准电压源。

电源要求如下:AVCC = 5 V, VDRIVE = 2.3 V至5 V(取决于外部逻辑接口要求)。

本电路笔记描述一个评估板的布局和性能,其中内置两个AD7606,构成一个16通道数据采集系统。为实现良好的通道间匹配和器件间匹配,模拟输入通道和器件去耦的对称布局非常重要。所示数据支持利用图1所示16通道ADC实现的匹配性能。

图1. 采用两个AD7606 8通道DAS的16通道、16位数据采集系统

16通道DAS的双路AD7606板布局

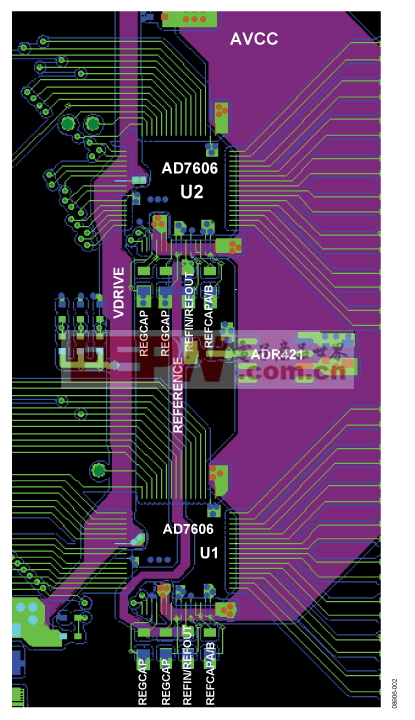

在内置多个AD7606器件的系统中,为确保器件之间的性能匹配良好,这些器件必须采用对称布局。图2显示采用两个AD7606器件的布局。

图2. 采用两个AD7606的16通道DAS的PCB布局

AVCC电压平面沿两个器件的右侧布设,VDRIVE 电源走线沿两个AD7606器件的左侧布设。基准电压芯片ADR421位于两个AD7606器件之间,基准电压走线向上布设到U2的引脚42,向下布设到U1的引脚42。使用实心接地层。这些对称布局原则适用于含有两个以上AD7606器件的系统。AD7606器件可以沿南北方向放置,基准电压位于器件的中间,基准电压走线则沿南北方向布设,类似于图2。

良好的去耦也很重要,以便降低AD7606的电源阻抗,及其电源尖峰幅度。去耦电容应靠近(理想情况是紧靠)这些引脚及其对应接地引脚放置。

REFIN/REFOUT引脚和REFCAPA、REFCAPB引脚的去耦电容是攸关性能的重要电容,应尽可能靠近相应的AD7606引脚。可能的话,应将这些电容放在电路板上与AD7606器件相同的一侧。图3显示AD7606电路板顶层的建议去耦配置。所示的四个陶瓷电容是REFIN/REFOUT引脚、REGCAP引脚、REFCAPA引脚和REFCAPB引脚的去耦电容。这些电容沿南北方向放置,以便尽可能靠近相应的引脚。

图3. 顶层去耦,显示了两个REFCAPA引脚、REFIN/REFOUT引脚和REFCAPA/B引脚的去耦电容

评论