基于Virtex-5的PCI-Express总线接口设计和实现

0 引言

PCI Express总线是新一代的I/O局部总线标准,是取代PCI总线的革命性总线架构。PCI总线曾经是PC体系结构发展史上的一个里程碑,但是随着技术的不断发展,新涌现出的一些外部设备对传输速度和带宽有更高的要求,PCI设计之初并没有考虑这些因素,因此并不能完全满足这些外部设备的需求。PCI Express总线正是在这种背景下应运而生的。

一个PCI Express连接可以被配置成x1、x2、x4、x8、x12、x16和x32的数据带宽。Xilinx公司的Virtex5系列FPGA芯片内嵌PCI-Express-Endpoint Block硬核,为实现单片可配置PCI-Express总线解决方案提供了可能。

本文在研究PCI-Express接口协议和PCI-Express Endpoint Block硬核的基础上,使用Virtex5LXT系列的XC5VLX50T FPGA芯片设计PCI- Express接口硬件电路,现YPCI-Express x4总线数据的传输。

1 PCI-Express总线概述

PCI-Express是一种高性能、通用的I/O互连技术,可以广泛应用于计算和通讯的平台。与传统的PCI/PCI-X总线相比,PCI Express用高速串行接口替代了PCI-X的并行接口;用点到点的基于Switch的交换式通讯替代了PCI-X的基于总线的通讯;用基于包的传输协议(packetbasedprotocol)替代TPCI-X的基于总线的传输协议。此外,它还引入了一些新的特性:更强的电源管理、服务质量控制(QoS),支持热拔插,以及完善的错误处理和恢复。

1.1 PCI-Express设备/拓扑结构

PCI-Express的典型拓扑结构如图1所示。PCI-Express协议中共定义了三种设备:RootComplex、Endpoint和Switeh。

Root Complex在系统中的位置类似于PCI-X中的主桥,它是I/O层次的根,它将CPU和MM连接至I/O部件。每个Root Complex可以有一个或多个PCI-Express Port(Root Port),每个接口定义一个层次域。Endpoint是PCI-Express的端点设备,可以分为PCI-Express Endpoint和LegacyEndpoint两类。

Switch是PCI-Express的交换设备,可以理解为逻辑上由多个PCI-PCI桥组合而成,每个桥对应于一个SwiSh端口。从配置软件来看,Swi-tch是两个或更多个逻辑的PCI-PCI桥。

1.2 PCI-Express的层次

PCI-Express协议中定义了三层结构:事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer)。其结构如图2所示。

事务层主要负责组包和拆包,负责管理基于信用的流控制。

数据链路层主要负责链路的管理和数据完整性的管理,包括错误的检测和错误的纠正。

物理层包含接口的所有电路:驱动器和输入缓冲、并-串/串-并转换、锁相环、阻抗匹配电路,具有接口初始化和维护的功能。物理层可以更进一步细分为逻辑物理层(Logical Physical Layer)和电气物理层(Electrical Physical Laycr)。逻辑物理层在发送方向上负责从数据链路层接收包,处理后发送上链路;在接收方向上负责将从链路收到的包经过处理转发到数据链路层。电气物理层是连接到链路的模拟接口,包含每个通道的差分收发器。

1.3 PCI-Express的包

对应于协议定义的三层结构,PCI Express定义了三种包:

(1)TLP:对应于事务层,主要完成协议中定义的存储器事务、I/O事务、配置事务和消息事务。

(2)DLLP:对应于数据链路层,主要用于链路管理的功能,包括和TLP确认相关的ACK/NAK协议、电源管理和流控制信息的交换。在这一层提供了点到点的链路重传机制和链路层的ECC校验,从而提供了可靠的容错机制。

(3)PLP:对应于物理层,能够支持物理层的链路训练,时钟容忍/补偿,自治的硬件电源管理。

2 Virtex-5 Lxt简介

综合考虑了实现PCI Express总线的周期、难易、成本等因素,最后本文采用了Xilinx公司65nm工艺的Virtex5 LXT系列芯片来实现PCI-Express的总线接口以及应用。

Virtex 5 Lxt PCIE Endpoint block具有PCI-Express的完整功能,完全符合PCIe基本规格v1.1版要求,作为FPGA内部的硬核,它是可配置的PCIe端点解决方案,大大增加设计的灵活性,降低设计的RNE费用,并且支持1x、2x、4x或8x通道的实现,为系统的功能扩张提供了有效的途径。

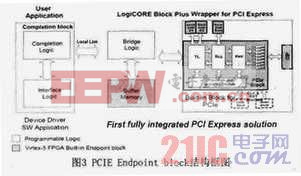

该系列芯片内嵌PCIE Endpoint block集成了PCIE协议中的物理层(PHY)、数据链接层(DLL)和传输层(TL),同时它还实现了PCI-Express设备的功能配置寄存器,其结构框图如图3所示,包含有以下几个接口:时钟和复位接口、配置和状态接口、电源管理接口、用户接口和传输层接口。该PCIE Endpoint block完成了PCI-SIG兼容性专题研讨会的严格测试步骤,保证了产品的兼容性,降低了风险;集成了Rocket IO-TMGTP收发器,该GTP收发器能提供100Mb/s到3.2Gb/s的串行连接性能,可以支持PCI-Express协议所需的2.5Gb/s的速率,与PCI-Expre-ss协议每通道2.5Gb/s工作模式兼容,这使得它在数据的编解码上满足PCI-Express协议的要求。本文使用该系列中的XC5VLX50T芯片设计PCI-Express接口硬件电路,实现PCI-Express x4的数据传输。

评论