一种新型扫频仪的设计

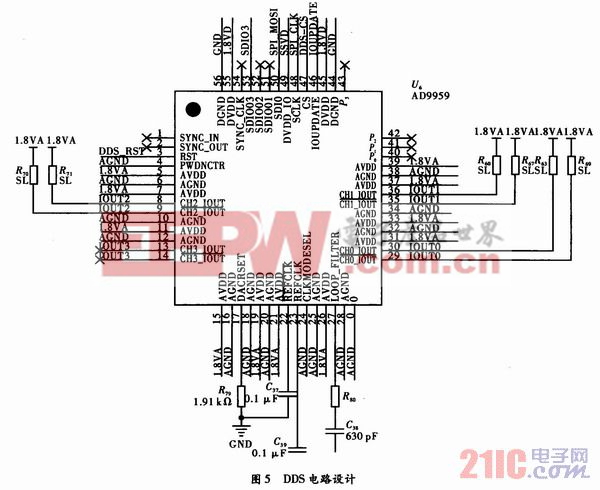

系统选用25 MHz有源晶振,通过设置寄存器中的倍频参数,使AD9959内部的锁相环电路倍频产生500 MHz的系统时钟,这一设置在DDS上电复位后完成。参考AD9959的技术手册,设计电路如图5所示。本文引用地址:http://www.eepw.com.cn/article/150589.htm

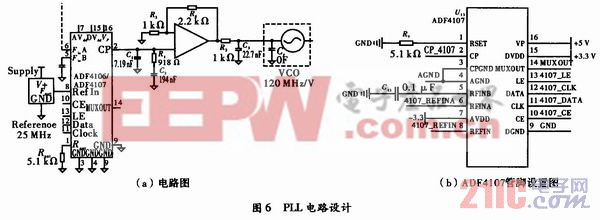

设计锁相环电路,对DDS输出信号完成32倍频,频率步进为10 Hz。后续混频电路将该路信号作为本振信号,所以其相位噪声和杂散指标对最终输出信号的相位噪声以及杂散有着直接的影响。考虑鉴相频率范围、相位噪声等指标,设计选用Analog Devices公司的PLL频率合成器ADF4107。ADF4107由低噪声数字鉴频鉴相器、精密电荷泵、可编程参考分频器、可编程A和B计数器以及双模预分频器(P/(P+1))组成。A(6位)、日(13位)计数器与双模预分频器(P/(P+1))配合,可实现N分频器(N=BP+A)。此外,14位参考分频器(R分频器)允许PFD输入端的REFIN频率为可选值。如果频率合成器与外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环。ADF4107最高鉴相频率为104MH z,相噪基为-219 dBc/Hz,采用ADIsimPLL软件可以方便的仿真并设计出外部锁相环路滤波器。

4 结束语

该扫频仪系统采用DSP+FPGA结构的设计方案。信号源是设计中的一个重要环节,决定了整个系统的指标和设计复杂度。本文在介绍PLL和DDS原理的基础上选用DDS激励PLL完成射频扫频信号源的设计,充分利用了DDS输出频率的灵活性和高分辨率,以及PLL电路的高输出频率,实现了优势互补。

评论