一种新型扫频仪的设计

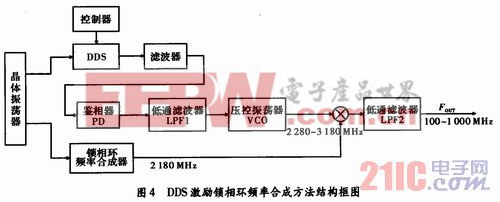

DDS激励锁相环方式电路简单,但是DDS的杂散和相位噪声在带内被恶化,其频率分辨率也会由于PLL的倍频作用下降到原来的1/N。PLL内嵌DDS难点在于系统中的带通滤波器很难实现,杂散抑制也难以获得比较高的指标。设计要求实现100~1 000 MHz的全程扫频信号源,而环外混频方式只能在一个较窄的频率范围内实现。综合考虑成本及电路实现的难易程度,该方案选择DDS激励锁相环的方式实现射频扫频信号源的设计。由于输出的频段较宽,将频段搬到较高的频段实现,降低相对带宽,然后下混频得到所需频段。实现原理框图,如图4所示。本文引用地址:http://www.eepw.com.cn/article/150589.htm

3 扫频信号源电路设计

设计使用晶体振荡器,一路由锁相环频率合成器产生2180 MHz信号作为混频射频信号,可以选择博威公司的固定锁相频率源MPS2180;另一路由主控芯片DSP控制DDS产生71.25~99.375 MHz的信号,经过滤波之后由PLL电路锁相至2 280~3 180 MHz。低通滤波器(LPF2)的作用是滤除混频后产生的高频分量,采用Mini_Circuits公司的低通滤波器LFCN-1400,通带范围DC~1 400 MHz,在1 000 MHz时的插入损耗为0.41dB。

AD9959是Analog Devices公司生产的一款高采样频率、高精度的DDS芯片,由4个直接数字频率合成器内核构成,每个通道均可提供独立的频率、相位和幅度控制。最高采样频率500 MHz,最高输出时钟频率250 MHz,频率分辨率可达0.12 Hz,能够满足系统的设计要求。设系统时钟为Fs,FTW为频率控制字,则DDS输出频率与控制字的关系为

![]()

评论