一种新型扫频仪的设计

2.2 数字PLL技术

锁相频率合成是利用锁相环路(PLL)技术实现频率的加、减、乘、除,主要由鉴相器(PD),环路滤波器(LF)和压控振荡器(VCO)组成。锁相环原理如图2所示。本文引用地址:http://www.eepw.com.cn/article/150589.htm

PD检测f1与f2相位差,输出平均值与该相位差成比例的直流电流。PD产生的脉冲电流经过LF产生调节电压,该电压驱动VCO来增加或减小输出频率直到PD平均输出为零。输出信号FOUT为

![]()

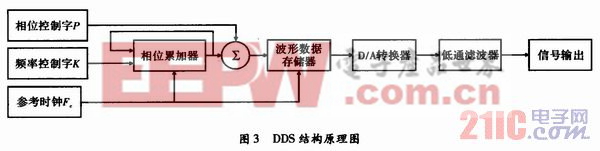

2.3 DDS技术

DDS技术从相位的角度出发直接进行频率合成,能够实现较高的频率分辨率和较快的频率转换时间,典型的DDS由相位累加器、波形存储器、数模转换器、低通滤波器和参考时钟FC这5部分构成。其结构原理框图如图3所示。

经过对频率控制字K的线性累加,最终得到其输出频率FOUT与时钟频率FC之间的关系

![]()

其中,N为相位累加器的位数。

当K=1时,得到DDS的频率分辨率为FC/2N。DDS技术有多种硬件实现方式,为了达到功耗低、集成度高且便于调试的设计目标,现代频率合成系统常采用专用的DDS芯片完成设计。

2.4 DDS+PLL结构的频率合成法

由PLL工作机理可知,当输出频率和分辨率越高时,倍频次数N很大,相位噪声恶化。而全数字结构的DDS也有不足:输出频率低,输出谱中杂散多,故难以应用于射频频率段。适当地组合PLL和DDS技术实现优势互补,可以使合成信号兼顾两者的优点,DDS+PLL频率合成主要有3种:(1)DDS激励锁相环;(2)PLL内嵌DDS;(3)PLL与DDS环外混频。

评论