AT91FR40162与cyclone2在工业控制的结合

工业控制中往往需要完成多通道故障检测及多通道命令控制(这种多任务设置非常普遍),利用ARM芯片与FPGA相结合来扩展检控通道是一个非常好的选择。这里介绍用Atmel公司ARM7处理器(AT91FR40162)和ALTERA公司的低成本FPGA芯片(cyclone2)结合使用完成多通道检控任务的一种实现方法。

各部分功能简介

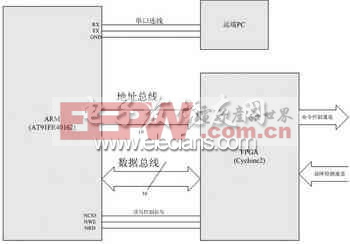

图1为此系统的结构连接框图。如图所示,ARM芯片与FPGA芯片之间通过数据总线、地址总线及读写控制线相连,而与终端PC则通过串口通信;FPGA与目标设备通过命令控制总线和故障检测总线相连。

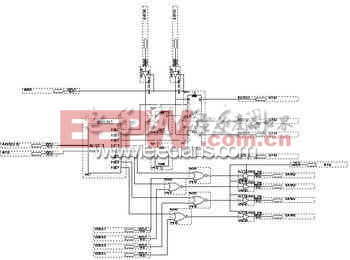

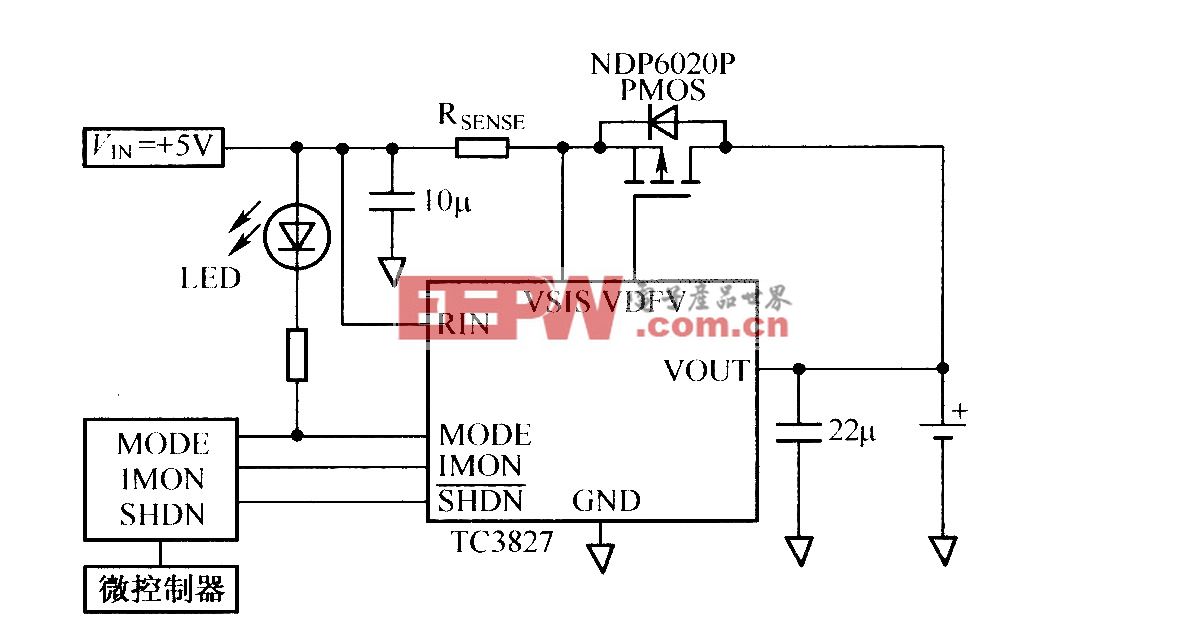

图2 FPGA内部逻辑结构

ARM芯片的ADDR2~0位地址线和片选使能信号一同进入译码器decode1进行地址译码后产生8路输出(FPGA内部可设置一个最大输出为256路的译码模块,所以在实际应用中可扩展为更多通道),低4路用于命令发送通道,高4路用于故障检测通道,读写使能信号控制数据总线。

ARM芯片接收到发送信号编码命令时,立即在串口接收中断服务子程序中并送相应地址(通道编号)和数据(命令状态)到FPGA中。译码器有效输出作为相应通道D触发器的锁存时钟,而数据状态则被触发器锁定后作为所选通道的输出完成相应控制。

ARM芯片在定时中断产生进入服务程序后对所有检测通道轮流查询,查询到有通道故障时,故障信号结合选中通路信号经与非运算送往数据端口被读取。

FPGA程序设计注意问题

1延时的配置

通过地址总线和数据总线进行命令传输和故障检测时,FPGA是作为ARM芯片的普通外设来使用的。而ARM芯片对外设访问的速度要远低于片内存储器,所以要在ARM中设置访问的正确等待周期。ARM中提供的延时周期为0~7个,通过调试即可找到外设合适的等待周期,此系统的等待周期根据实际测试设置为5个,具体的配置方法见ARM程序说明。

2 读写使能信号的连接

从图2中可以看出,写使能信号NWE及读使能信号NRD应作为数据线(DATA0~5)的三态控制信号连接,即使在ARM芯片无其他外设时也不能缺省。因为ARM的上电加载程序时间要长于同一系统上FPGA的程序配置时间,而FPGA的检测及控制通道与ARM芯片的数据总线相连,FPGA加载完成后数据总线会存有相应通道的逻辑电平值(不为三态),这就会导致ARM芯片在对片内Flash芯片烧写程序或上电加载程序时与FPGA冲突(数据被逻辑锁定),造成无法正确定位操作对象而使读写失败。

ARM配置及应用程序说明

1 处理器的资源分配

● 存储器

AT91FR40162内嵌一个256KB的SRAM,1024K个16位字组成的Flash存储器。SRAM通过内部32位数据总线与ARM核相连,单周期访问,Flash存储器则通过外部总线访问。

● 系统外围

EBI:外部总线控制接口,EBI可寻址64MB的空间,通过8个片选线(NCS0~NCS3独立)和24位地址线访问外设,地址线高4位与片选线(NCS4~7)复用,数据总线可配置成8/16位两种模式与外设接口。

PIO:并口控制器,PIO控制32根I/O线,多数为复用引脚,可通过编程选择为通用或专用。

AIC:先进中断控制器,实现片内外围中断及4个外部中断源中断的管理,其外部中断引脚与通用I/O复用。

● 用户外围

USART0~1:串口收发控制器,支持8个数据位的发送,可以进行异步/同步传输选择,其片外引脚与通用I/O复用。

TC:定时/计数器,可以产生定时中断和计数功能,其片外引脚与通用I/O复用。

2 存储器地址重映射后的空间分配

在CPU上电后,都会从地址0开始第一条指令代码的执行,而上电复位后0地址必须映射到NCS0片选所接的器件上,这里必须将NCS0连接到片内Flash上以加载初始化程序和应用程序。由于中断和异常的入口地址是0~20H固定不变,它们的产生都是跳转到0~20H之间相应的地址取程序执行,为了加快中断响应,必须将0~20H地址映射到片内RAM区,所以在初始化的重映射命令执行(EB1_RCR的RCB位置1)后,内部RAM就映射到地址0,所有的中断入口响应和堆栈操作都被映射到在RAM区进行。

由于重映射主要是用于Flash和片内RAM的地址空间交换,所以片内外围接口(EBI、USART、TC)对应的存储器编程地址范围在映射前后不发生改变,而访问外设地址为重映射后所分配。重映射后地址分配如表1所示。

3 应用接口的存储器配置

EBI存储器:在8个EBI片选存储器(EBI_CSR0~EBI_CSR7)中设置外设访问参数。其中,32位存储器中包括数据总线宽度8(16)设置,等待状态数目1~7个周期设置,等待使能(不是使能)设置,片选使能(不使能)设置。这里将FPGA作为外设,使能NCS3(也可根据实际选择其他空闲片选线),选择总线宽度16,使能等待周期并设周期为5(根据调试选择)。因默认NCS0为加载Flash片选线,而Flash为16位信号、7个等待周期,故需在EBI_CSR0中选择16位总线宽度、7个等待周期并使能NCS0。

AIC存储器:AIC存储器管理所有内外部中断,对此存储器的正确初始化赋值才会打开相应中断。设定AIC工作参数:应用串口通信模式为异步模式,串口发送的数据位字符长度为8位,通信的波特率9600B/s,串口中断优先级为6(中断优先级由低到高0~7),接收发送通道使能。

TC存储器:定时中断存储器需要设定定时长度为1s(每1s产生中断进行故障查询),定时通道使能及软件触发模式,定时中断优先级设为1。

评论