基于FPGA的二次群数字信号分接部分功能实现

6.结论

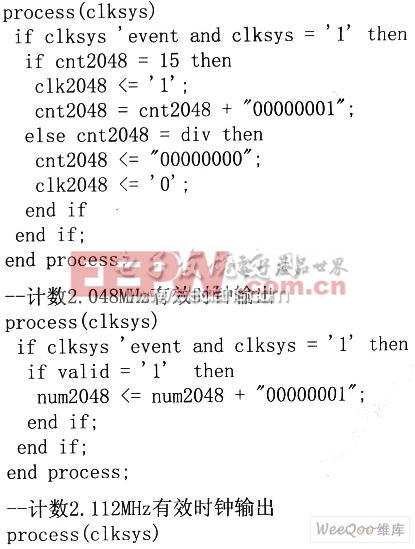

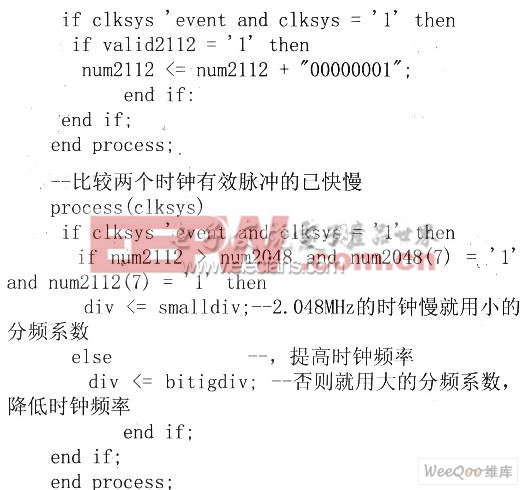

本文对二次群的分接处理,提出了一种基于FPGA的方案,介绍了二次群的帧结构,给出了帧头捕获、帧丢失告警、负码速调整等VHDL语言的关键程序。在QUART

UART即为Universal Asynchronous Receiver/Transmitter,译为通用异步收发器。UART是设备间进行异步通信的关键模块,用于控制计算机与串行设备的芯片。它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。

USII软件中编译完成,资源仅占用三十多个LE,给二次群设备的设计提供了一种参考,具有很高的应用价值。

评论