基于FPGA PCI的并行计算平台实

本文介绍的基于PCI总线的FPGA计算平台的系统实现:通过在PC机上插入扩展PCI卡,对算法进行针对并行运算的设计,提升普通PC机对大计算量数字信号的处理速度。本设计采用5片FPGA芯片及相关周边芯片设计实现这一并行高速计算平台,并在该平台上完成了DES和MD5等算法的加密和解密。文中通过基于MD5算法设计的加密方案(仿Yahoo邮箱的密码校验)进行暴力破解,验证了本系统的可行性以及速度快、性价比高等显著优点。

本文引用地址:http://www.eepw.com.cn/article/150290.htm1 系统结构

系统利用普通PC机或工控机进行控制、数据流下载和结果采集,大计算量的数字运算利用IP-CORE技术并行地在FPGA中进行。将数字信号处理的算法设计为一个单元模块,并根据芯片的结构对布局和布线进行优化,该单元模块重复利用的技术被称为IP-CORE技术。在本系统中利用TP-CORE的可重复利用性,通过仲裁逻辑调度数据的分配,从而实现算法的并行处理。

1.1 硬件结构

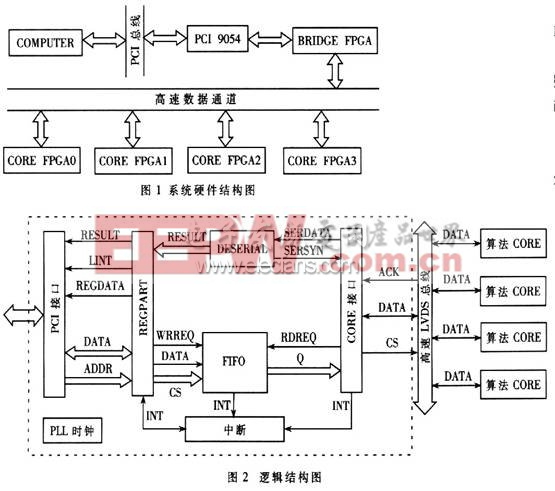

系统中采用5片ALTERA公司的STRATIX EP1Sl0FPGA芯片,其中4片作为数字信号处理算法CORE的载体(文中称为算法FPGA);l片作为连接PC机与运算CORE的桥接芯片、加载程序、并行总线裁决和中断判决等仲裁逻辑的载体。与PCI总线的接口使用PLX公司的PCI9054芯片。系统硬件结构如图l所示。

1.2 逻辑结构

1.2 逻辑结构BRIDGE FPGA的程序采用自顶向下的设计方法,其逻辑结构如图2所示,按功能可分为以下部分:顶层模块PCI_FPGA_PARALLEL;与PCI9054的接口模块PCI接口;数据缓存及仲裁部分:数据缓存模块FIFO、寄存器模块regpart、数据回传模块deserial、内部总线仲裁和流控模块CORE接口等。

PCI接口部分实现与PCI9054芯片的接口时序,使得复用的地址和数据分开,产生地址空间的选取及使能信号,便于后端处理。

仲裁逻辑部分:

(1)实现对地址空间内数据缓冲区、各种寄存器的读写,以及根据配置寄存器的内容对算法CORE和桥FPGA做相应的操作(配置、启动、停止、复位等)。

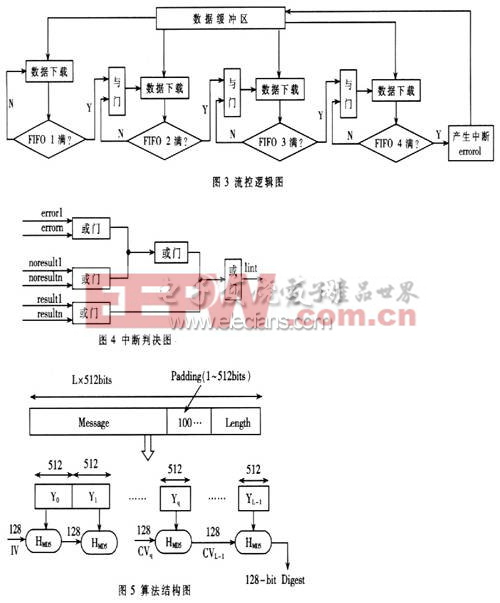

(2)利用缓冲区及FIF0的队列长度信号wrusedw、rdusedw、full和empty进行数据流控制。数据由PC机下载时首先进入缓冲区,每一块算法CORE均对应一个数据下行FIFO,由FIFO当前状态来判定是否从缓冲区中取数。具体逻辑模型如图3所示。

(3)返回结果引入本地中断机制,当有正确结果产生、或无正确结果但密钥匹配完成、或系统异常状态,均产生中断信号并填写中断类型寄存器,经级联后产生向PC机的中断。中断判决如图4所示。

评论