PLD和数据通路来释放微控制器中CPU资源

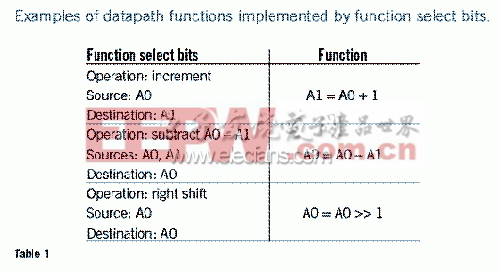

根据数据通路的具体设计,其可能会做一系列复杂操作,如表1显示。

这个函数选择模块实际上可以是一个小容量的SRAM,预加载所需的函数选择位,SRAM的地址线可以用来选择运行哪个操作。最后,多数据通路可以用进位和移位信号链在一起,以便可以进行多字节操作数。

由于数据通路只有少数特定功能函数,很容易优化设计,因此其创建成本较低。然而,对于实现复杂的逻辑,数据通路远远没有PLD那么灵活。那么,对于创建智能、灵活、低成本的数字外设来说,哪一种方法是更好的呢?是PLD还是数据通路?答案是,将两者相结合。下面是一个实例,来看看是如何实现的。

通用数字模块

同时使用PLD和数据通路的系统实例是赛普拉斯半导体的PSoC3和PSoC5芯片。每个系统包含最高24个通用数字逻辑子系统,称为通用数字模块(UDB),其结构如图3所示。一个UDB包含两个图1所示的PLD,一个数据通路以及状态机和控制寄存器。有两个链路路径,一个用于PLD,一个用于数据通路。由一个路由通道来连接各UDB子块之间以及UDB之间的信号。PLD配置、数据通路和路由通过写入UDB配置寄存器来实现。

UDB的PLD设计在图1中进行了描述。如图4,UDB数据通路类似于图2所示的基本的数据通路,但是它更精密复杂,因为拥有更多寄存器和更多的功能。

图4:UDB数据通路框图。

* 8位ALU可以实现所有的七个基本函数—递增、递减、加、减、与、或以及异或,并且它有单独的位移和位掩码模块来进行ALU结果后处理(8位ALU传输功能只需通过ALU传送一个值到位移和位掩码模块)。位移模块可以做左位移、右位移、半字节交换和传输。掩码模块可以和单独的掩码寄存器里的内容逐位相与(图中未显示)。

* 操作可以使用两个累加器(A0,A1)和两个数据寄存器(D0,D1)来完成。两个FIFO寄存器(F0、F1)可用来在数据通路和CPU之间传输数据。FIFO深度可达4字节。这一结构可以使多任务处理变得简单;在不同的时间,独立操作可以在寄存器子集完成。例如,A0、D0、F0可以用于一个任务,而A1、D1、F1则可用于不同的任务。

* 广泛的状态条件(例如:比较、零检测、所有个体检测、溢出检测)可以应用到累加器,数据寄存器,以及路由到器件其它地方。

评论