基于高速USB接口模块的数据采集系统

引言

本文引用地址:https://www.eepw.com.cn/article/149482.htm工程师在设计基于PC的数据采集系统时都认为,要想获得比较好的性能,都需要使用PCI总线。其实并不是这样,随着USB通信技术的不断发展,USB总线的传输速度和可靠性都在逐步提升。对于广范应用的USB2.0,其最快速度能够达到480 Mb/s。就算其中一些中断或者协议占用一部分带宽,高于80 Mb/s的速度也是很容易实现的。而USB3.0协议下的理论速度可以达到USB2.0的10倍左右。另外,相比于PCI卡,USB接口对系统的开发与升级更加方便。

QuickUSB[1]是基于CY7C68013A[2]开发的一款针对USB2.0的高速USB模块。Bitwise公司为这款模块提供嵌入EEPROM的底层程序,同时还在PC端提供了相应的LabVIEW和C语言的API底层程序,这为系统的开发提供了很大的便利。本文设计的系统[3]就是基于这个原理。

1 硬件电路设计

系统的核心硬件是FPGA、ADS803E、CY7C68013A以及Bitwise公司的内嵌底层程序的EEPROM。

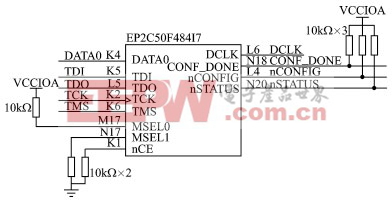

图1是FPGA的配置电路。CY7C68013A可以通过PS模式来配置FPGA,而不需要其他的下载器。系统选择的FPGA型号是EP2C50F484,为了使用PS模式下载,需要分别设置MSEL0=1,MSEL1=0,MSEL2=0。注意配置端口需要增加上拉电阻来保证其正常工作。

图1 FPGA的配置电路

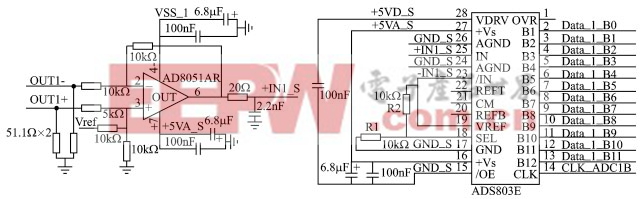

系统选择ADS803E作为ADC转换电路,ADS803E的转换速度可以达到5 MHz,而且其引脚与同类型的10 MHz的ADS804以及20 MHz的ADS805兼容。图2是系统ADC转换电路。

对于ADS803E的输入信号首先要经过一级运放跟随,目的是为了将输入信号控制在其测量范围之内。ADS803E的测量范围可以通过改变图中电阻R1与R2的值来实现,其量程范围为0~2×R1+R2R1。ADS803E的输出要在6个时钟之后才会有效,也就是说其数字输出对于模拟输入存在6个时钟的延时。同时,为了减小系统的功耗,在不需要进行ADC转换的时候,可以通过FPGA将ADS803E的时钟停止。

图2 ADC转换电路

评论