设计合理的高速总线测试方法

就在几年前,许多设计工程师还在苦苦挣扎于步履沉重的总线和I/O速度,而每12~18个月各种处理器的运行速度就增加一倍。而后,几乎是一夜之间,总线和I/O技术开始发生变化。速度加倍,而后又增加一倍。紧接着,如源同步时钟等新型解决方案和低压差分信号(LVDS)的小数据有效窗带来的挑战,使测量、验证和确认比以往更为重要。而带来此性能提高的完全相同的力量,也使插入测试设备变得更具有侵略性。

但现在已有新的工具和方法,可尽量减少对设计的影响。然而,现在必须在设计的最初阶段就仔细地对测试进行规则。如今不再有可能建造一个原型,而后简单地在线上进行焊接以连接示波器或逻辑分析仪,测试方法必须是整个设计规划中的一部分。

不幸地是,数字设计工程师已采用多年的技术和工具不再可行。现今的设计工程师如果不广泛建模和采用Spice仿真,甚至根本无法想像进行每秒千兆位总线的设计。当然,其中也不乏有人继续用与4MHz处理器的黄金时期同样的工具和方法,试图对高速电路进行故障定位和调试。

为实现速度上的突破,HyperTransport、InfiniBand和RapidIO等技术,采用了如LVDS等“新”电气规范,并以高效点对点总线结构替代了传统的多点接入(multidrop)总线。突然间,数字设计工程师从舒适的0和1的世界,转而挺进到高频模拟世界。那些在场与波里上了第一课,而后在黑夜中惊呼,现在正在被拉回传输线理论、反射以及甚至是S参数的真实课堂。

由于当今总线的高频效应和新型拓扑结构,设计工程师需要更有效地使用测试设备,以确定信号完整性和数据完整性。同时,仿真和评估工具不断成熟与改进,新型总线技术局限了那些工具的使用。

例如,模型是从学习和观察开始构建的。当市场上出现新型总线时,提供给大多数工程师的信息十分有限。大部分情部下,领先的技术采用者把它们当作其知识产权,在技术成为主流技术之前,不愿与人分享信息。所以,在采用这些技术的初期,测试工具和采用工具进行调试和确认的能力十分关键。

利用老式4MHz微处理器或USB1.1设备,100MHz示波器或任何示波探测手持装置就足够用了。它们可以应付1.5Mbps/或甚至12Mbps的设备。而对480Mbps USB速率来说,如示波探测这样简单的事情都会动态影响到系统。

测试设备测量选择对如通过1GHz时钟“两级泵激”(double-pumping)数据的HyperTransport链路这样的先进系统有多大影响呢?由于创建与保持时间减少,数据捕获尤其受到影响。事实上,新技术的出现已带来了新的术语。创建与保持时间现在已经是过时的术语了。现在,高速数据传输被称为“数据有效窗”,它是创建、保持和压摆的结合。

想当初,1992年的Intel Pentium前端总线(FSB)具有5ns的创建时间和5V的压摆。现在,InfiniBand和RapidIO的数据有效窗为250ps,差分压摆为200mV。

相较于1992年Intel FSB,现在InfiniBand规格数据有效窗减小20倍,压摆减少25倍,delta值为500。换而言之,当今的总线仅消耗了1992年Pentium FSB 0.2%的能量。

从传统多的多点接入总线到点对点技术的变化带来了另一个挑战。多点接入总线的最佳实例是PCI总线。采用了多个连接器,对总线进行探测相当容易。测试工具或测试连接被插入一个连接器,留下其他连接器以供插入真正的设备。

但是HyperTransport规范甚至没有包括一个连接器。那么设计工程师如何对总线进行探测呢?这种挑战并不仅限于HyperTransport。运行于133MHz的 PCI-X也只有一个插槽,如果插入了测试工具,该插槽也无法再提供真正的设备使用了。

PCI-X和Accelerated Graphics Port2.0(AGP4X)的解决方案为一种内插板设计。这是一块插入主板上的连接器的卡板,同时为应用设备提供连接器以及为逻辑分析仪提供通道。该解决方案要求极其仔细的内插板设计,以防止信号歪斜和对目标系统产生负载。

内插板设计方法在高达133MHz时钟速率工作良好,甚至对于如266MTps DDR SDRAM数据两级泵激系统都是一种非常稳定的设计。然而,随着技术跃进到533MTps或更高,内插板设计变得太具侵略性,并将产生负载、反射、分支短根(STub)和不可接受的通道延迟。

现在存在一个难题。新技术意味着仿零点和模型没有提供让人对产品产生信心的足够的技术细节。因而,物理测量非常关键,不过通过连接器的简单连接不再可行了。

下面两个实例显示了解决连接难题的不同解决方案。一个实例考察怎样针对HyperTransport链路设计连接器,另一个则检查内插板式解决方案不再可行的AGP3.0端口。两个方案都被开发用以支持分析探测的连接。在每种情况下,设计工程师进行广泛的Spice仿真,以及实实在在的物理验证,以证明所述连接解决方案要的有效性和可靠性。

HyperTransport

作为一个创新型的串行连接接口,HyperTransport可以在理论值为16GBps的速率传输数据。物理层采用了具有800mV压摆和200ps数据有效窗的LVDS信号技术。如前所述,由于HyperTransport没有任何连接器,它也提出了独特的挑战。没有连接器,对于问题根本原因的跟踪、对于复杂时序的捕获和对系统稳定性的确认,即使不是不可能的,也会变得很困难。

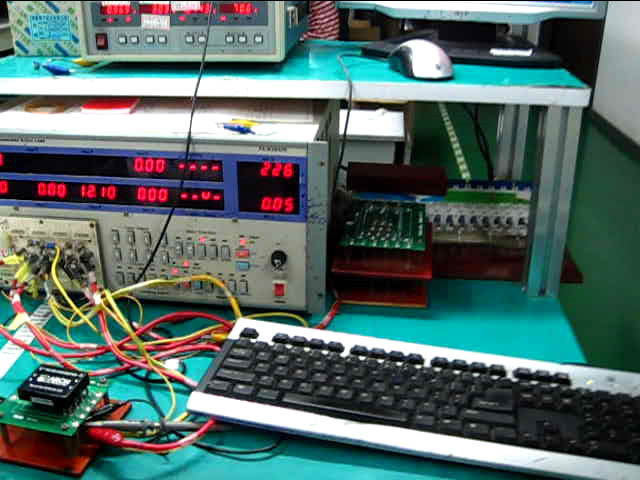

为了接入HyperTransport链路,连接器必须被设计到目标系统中。这里Spice模型显示了HyperTransport链路规范、80针RobinsON Nugent连接器和Future Plus FS2240 HyperTransport分析探测器的值。此例用于说明目的。

FS2240被设计用于对两台HyperTranspor设备之间进行采样。每一个单向连接链路安排一个探测连接。8b链路包括8个数据信令、1个控制信令和1个时钟信令,而16b链路包括16个数据信令、1个控制信令和2个时钟信令。目标设计的HyperTransport信号被通过孤立的尖端电阻连至探测器。当探测器附着于目标时,它在每个链路的差分对之间仅呈现标称负载。

利用前一代嵌入式总线,对于设计工程师而言典型的测试解决方案是,在板布局设计中包含一个测试连接器。在较低的频率上,所产生的分支短根(stub)对总线的影响极小。但在现今差分总线的频率上,分支短根就成为不可接受的反射源。一种简单的解决方案是对连接器连接端和链路之间,以尖端电阻器进行桥接。当不再需要测试连接时,只要去掉尖端电阻器以消除分支短根相关的问题。

当需要从设计走向制造时,只要不加载尖端电阻器和连接器,仅留下连接器的连接端。该解决方案还有一个隐藏的好处:如果产品在现场失效,或整个产品系列出现问题,很容易连至总线以验证操作。简单地加载连接器和尖端电阻,板就准备好可以进行测试了。

为使对目标HyperTransport的影响降至最小,必须仔细地将连接设计到电路中。这些通过采用Spice模型作为电路仿真的一部分而实现。正确的尖端电阻值、连接器的放置和线路长度,对于组合连接器和减小对链路的影响都很重要。目标设计要求包括:从驱动设备到连接器的延迟得到补偿;到连接器的最大刻蚀长度有限;从目标信号到尖端电阻器的分支短根长度最小。

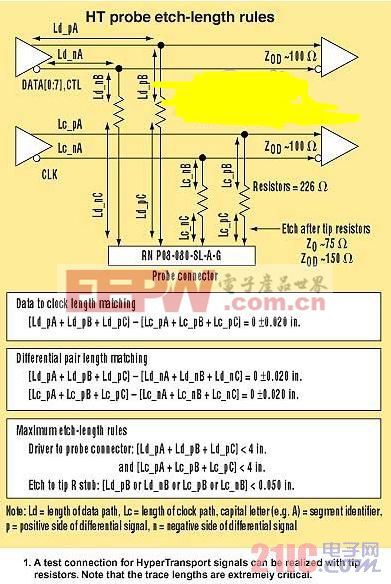

图1显示了从驱动器到的Robinson Nugent连接器的推荐的刻蚀长度。注意,在数据链路和时钟线之间线路长度之差必须在±0.02英寸范围内。还有,差分对之间的线路长度之差限制在±0.02英寸。总之,从驱动器到连接器之间的线路长度被定义在小于4英寸。

为帮助设计工程师对设计进行的优化,也确定了线路的阻抗值。在226Ω尖端电阻输入侧的最小信号电压应为550mV标称值,如HyperTransport规范。给出的值基于1GHz的时钟频率,如果时钟频率低于1GHz,可以采用更长的线路长度。

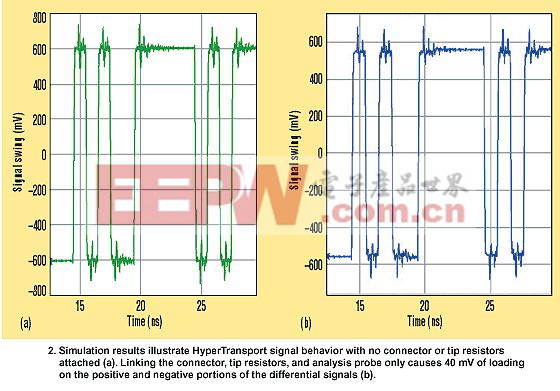

仿真得出的预计显示了设计中没有连接器或尖端电阻器的数据线的信号特性(图2a),和在设计中加入连接器和226Ω尖端电阻器的信号特性(图2b)。scope-like波形显示增加连接器、226Ω尖端电阻器以及我们的分析探测装置,导致小于7%的信号减弱。

如同工程学中的每件情一样,该解决方案也有折衷。它要求在板上留有空间以安装连接器,包括禁用区以连接FS2240测试连接器的外壳。选择80针RobinsonNugent连接器的原因之一在于它小巧的外型尺寸和高频特性。到目前为止,最大的折衷是在连接器内设计所要做的工作。

增加测试连接器要求进行规划。不事先考虑好就意味着你将无法对电路进行测试,或者你以后需要增加连接器。第一种情况将导致出售没有进行完整特性定义的产品,在第二种情况下,增加连接器会严重延迟产品开发。像生活中的大多数事情一样,开始时的一点点计划,将在后来节省大量的时间和金钱。

AGP3.0

这一代产品具有800mV压摆,266MTps(4X)和533MTps(8X)的数据速率。前一代产品AGP2.0具有266MTps最大数据速率,但压摆为1.5V。采用533MTps的速率,压摆减小50%,使采用AGP4X内插板极为困难,甚至是不可能的。

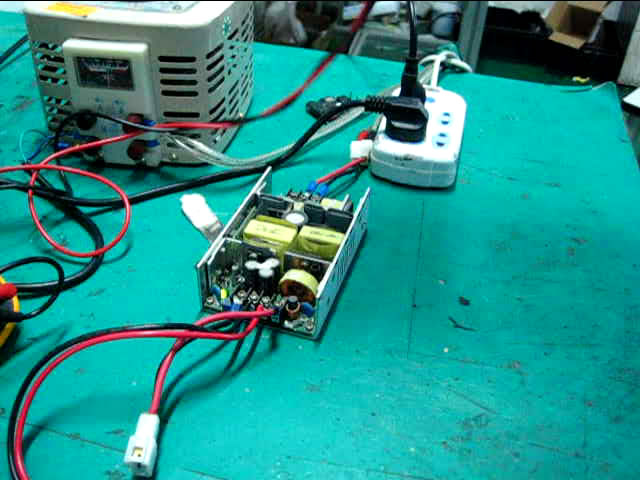

给定AGP信号特性和总线带宽,与针对HyperTransport所做的相类似,另一款连接器的设计将非常困难。所以,我们开发出一种独特的探测解决方案,利用现在PCI连接器的长处,同时防止了内插板可能引致的信号延迟和负载。

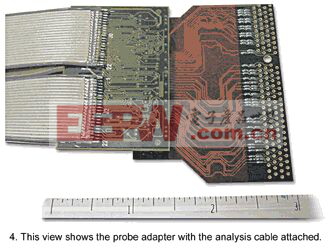

连接解决方案为一种柔性/局部柔性(stiffened-flex)性PCB,它直接焊接到目标AGP连接器后端(焊接端)。如图3所示,探测器适配器将包括独立的尖端电阻器和用于探测器线缆适配器的连接器,见图4的说明。

探测器适配器的所有元件安装在与目标相对的一侧,这支持了目标上适配器的嵌入安装。采用柔性电路以附着于连接器,最大限度地利用了板空间,并保持了信号的完整性。它也提供了一种能够被用于量产系统和原型板的连接系统。

该解决方案必须要求在目标AGP连接器附近有一小块元件禁用区。由于新型主板的密度增加,这一要求对于一些量产产品也许很困难。此外,从连接器的穿孔必须足够长以焊上柔性电路。一旦附着了柔性电路,就很难去掉而不在不经意之间损坏探测器适配器。这样,鉴于所有实际的原因,探针应当被当作消耗品。

|

评论