基于嵌入式的高速数据采集系统

1 系统结构

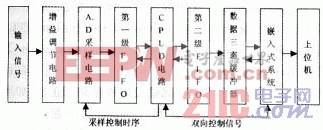

本文引用地址:http://www.eepw.com.cn/article/149285.htm高速数据采集系统由高速ADC、CPLD、FIFO和嵌入式系统组成,系统结构如图1所示。

图1 系统结构

2 嵌入式操作系统—Linux

Linux作为嵌入式操作系统有以下几大优点:

(1)可应用于多种硬件平台;(2)源代码公开;(3)微内核直接提供网络支持;(4)高度模块化使添加部件非常简单。

硬件设计

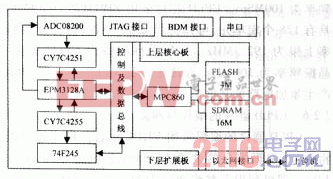

整个数据采集板采用双层设计,上层是嵌入式系统的核心板,包括嵌入式系统CPU、FLASH和SDRAM等系统基本配置。MPC860的控制总线与数据总线通过核心板100线×3的接口插座与下面的扩展板各芯片通讯。硬件的结构框图见图2。

图2 硬件框图

嵌入式系统的CPU选用Motorola的MPC860芯片。它内部集成了微处理器和一些控制领域的常用外围组件,特别适用于互联网络和数据通信。MPC860 PowerQUICC通信处理器可以根据用户的不同要求提供2~4个串行通信控制器、数据缓存,各种级别的网络协议支持。该处理器专为宽带接入设备如路由器、集线器、交换机和网关等设计。

系统内存

系统内存由3部分组成,MPC860内部集成了4KB数据Cache,以及片外扩展的Flash和SDRAM。Flash为2片Am29LV160D,总容量为4MB×8bit,用来存放ppcboot.bin和linux.bin文件。SDRAM采用2片K4S641632F,总容量为16MB×8bit。

通用外设

MPC860的4个串行通信控制器(SCC)支持以太网、HDLC/SDLC、HDLC总线(用以实现基于HDLC的局域网)、AppleTalk、UART、比特流透明传输、基于帧的透明传输(CRC可选)、支持PPP(Point to Point Protocol)的异步HDLC等标准协议,只需很少的外围芯片就可以实现串行口和USB Slave接口。MPC860外扩一片LXT905PC就方便地实现了一个10BASET的以太网接口。

嵌入式系统调试

MPC860处理器支持BDM(背景调试模式),完成板卡硬件检测、下载、运行、烧写FLASH、内核调试、单步调试等最底层的调测功能。在背景调试模式下,通过向CPU发送命令,可以实现对寄存器、系统存储器的访问。

另外,在调试时还可以使用Motorola公司的Power TAP Pro仿真器和Code Warrior IDE for PowerPC编译环境在windows下进行应用程序的开发和调试。

A/D转换和CPLD电路

A/D采样采用的器件为ADC08200,精度为8位,采样频率由20MSps至200MSps,本电路中的A/D采样频率为100MSps。CPLD芯片采用EPM3128ATC144-5,具有128个宏单元,可以提供2500个逻辑门,计数频率上限为192.3MHz。A/D采样时钟由CPLD提供。晶振频率为100MHz,直接接入到CPLD中,由CPLD产生累加电路的其他信号。

CPLD器件的编程与调试

CPLD器件的编程采用VHDL语言。程序经过逻辑综合(逻辑综合的软件为Altera公司的QuartusⅡ 4.0)后即可利用下载线通过JTAG(联合测试行动组)接口将逻辑综合生成的*.pof文件烧写到CPLD器件中,然后即可测试芯片的功能。

FIFO数据缓存电路

从图1可以看出,系统中包含两级FIFO。第一级FIFO芯片采用1片CY7C4251,容量为8KB×9bit,工作频率为100MHz。第二级FIFO采用2片CY7C4255并联,容量为8KB×36bit,但实际上只用了24bit数据宽度,因为8bit的A/D转换数据累加10000次,24bit就能满足系统的功能要求。

软件开发

该数据采集系统的软件编程包括两部分,一部分是MPC860嵌入式系统的编程;另一部分是CPLD的编程。关于CPLD的编程模式见2.2.6,这里只介绍嵌入式系统的软件开发模式。

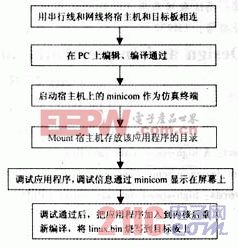

本系统采用交叉编译的方式进行Linux应用程序的开发和调试,先将应用程序在宿主机上调试通过后,再移植到目标板。这种模式适合于大型复杂的应用,优点是程序调试方便但移植需要做一些工作。其开发流程如图3所示。

图3 嵌入式系统的开发过程

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论