MIPS推出新一代Aptiv™处理器

为数字家庭、网络和移动应用提供业界标准处理器架构与内核的领导厂商美普思科技公司 (MIPS Technologies, Inc)日前宣布推出了新一代 Aptiv微处理器内核,包括 proAptiv、interAptiv 和 microAptiv 系列产品,可为 目标市场提供三种不同的性能水平。

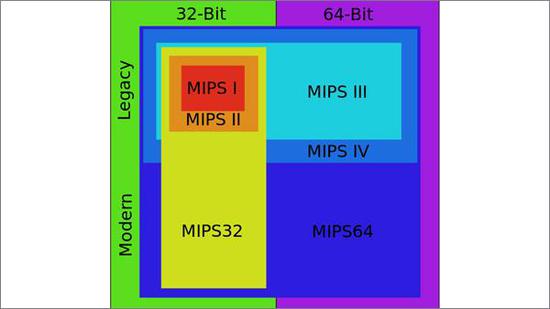

本文引用地址:https://www.eepw.com.cn/article/132541.htm基于MIPS32™ Release 3架构,这些新产品将增强 MIPS 在家庭娱乐和网络市场的领导地位,并向海量的嵌入式系统延伸,同时成为移动市场中富有竞争力的替代解决方案。对移动设备来说,Aptiv可为平板电脑和智能手机的应用处理器提供顶尖的多核性能,为基带处理提供高效的多线程技术,并为触摸屏控制器、SIM卡和安全、以及 GPS 等嵌入式控制和应用提供入门级性能。

ProAptiv 系列的重要特征:

- 领先的高端 CPU 性能与效率,超过4.4 CoreMark/MHz 和 3.5 DMIPS/MHz 1的性能,比同类竞争 内核IP 2相比明显更小的硅面积

- 是高端移动设备和智能家庭娱乐产品等联网消费电子产品的应用处理器和网络应用中控制处理器的理想选择

- 高效的顶级性能,可减少许多移动应用中诸如“big.LITTLE”等额外的电源管理设计开销

- 比老一代MIPS32 74K™/1074K™ 超标量单核/多核产品高 60%-75% 的 CoreMark 和DMIPS 分数

- 每个内核1 至多个线程高度可扩展,并能在多核同步处理系统(CPS)下实现最多可达六个内核的多核系统

- 主要的架构特性和增强功能:

o 高性能多发射、深度乱序执行架构以及先进的分支预测

o 新款更高性能的浮点运算单元(FPU),与内核 1 :1 的时钟频率,双精度执行

o 单核或多核(最多为 6核)配置

o 增强性能的紧耦合第二代一致性管理器和L2 二级高速缓存控制器,实现更低的系统总延时

o MIPS ASE v2数字信号处理(DSP)架构扩展

o 高效的增强虚拟地址(EVA),32位地址下实现3GB以上 的用户空间访问

interAptiv 系列的重要特性:

- interAptiv 内核采用平衡的9级流水线设计和多线程技术,可提供领先的性能与效率,能以比同类竞争内核更小的晶圆面积实现多出 50% 以上的 CoreMark/MHz

- 适合需要并行处理和对成本和功耗优化要求比较高的应用,如智能网关、LTE基带处理、SSD 控制器和汽车电子等

- 每个内核具备 1 至多个线程的可扩展性解决方案,并能在多核同步处理系统(CPS)下提供最多四核的多核方案

- 特性和增强功能:

o 多线程流水线实现了双虚拟处理器,可被 SMP Linux 操作系统视为两个完整的 CPU

o 硬件QoS、线程管理和线程间通信支持,能为实时应用实现最佳控制

o 增强性能的紧耦合第二代一致性管理器和L2 二级高速缓存控制器,实现更低的系统总延时

o 支持多达两个 I/O 一致性管理单元

o 内核和 CPS 级功耗管理

o L1 一级数据高速缓存、L2 高速缓存和数据 SPRAM支持 ECC

o 高效的增强虚拟地址(EVA),32位地址下实现3GB以上 的用户空间访问

o 可选的浮点运算单元

评论