Xilinx FPGA的Fast Startup

对于这种演示来说,我们使用带BPI的外置闪存作为配置接口。一旦初始高优先级比特流配置完该处理器子系统,在BRAM外运行的软件将初始化TFT控制器,并将数据写入DDR内存中的帧缓冲器。这样就能确保启动时屏幕迅速显示在TFT上面。之后,从BPI闪存中读出第二个比特流,并配置低优先级分区,这样处理器子系统可以运行其他应用程序,如Web服务器。

本文引用地址:http://www.eepw.com.cn/article/125814.htm为方便扩展和清晰隔离两个分区,我们使用了AXI至AXI桥接器。这也在最大程度上减少了穿过两个设计分区边界的网络。低优先级分区与高优先级分区共享系统时钟。

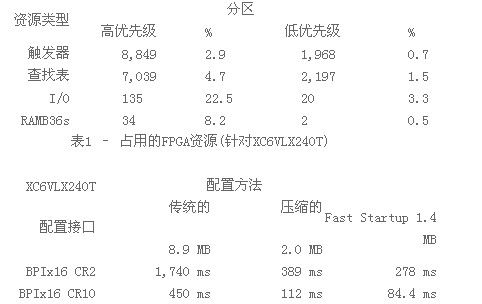

表1表示FPGA资源利用情况,表2表示传统启动方法、仅有高优先级分区压缩比特流的启动方法[6]和Fast Startup配置方法的配置时间。每种方法都使用BPIx16配置接口,而采用的配置速率(这个选项决定了目标配置时钟频率)为2 MHz和10 MHz。我们使用一台示波器测量了该数据,捕获了FPGA的“init”和“done”信号。 表2中“压缩的”一栏表示仅有高优先级分区的压缩比特流。含有两个分区的完整FPGA设计的压缩比特流将达到3.1 Mbyte。

表2 – 测得的配置时间(Virtex-6视频设计)

SPARTAN-6汽车ECU设计

为了验证针对Spartan-6的Fast Startup方法,我们选择了汽车领域的ECU应用情形。每当您在汽车电子控制单元中看到一个FPGA器件时,它一般都仅由ECU的主应用处理单元使用(见图5)。我们的目标是实现一种将系统处理器放入FPGA中的设计。这样我们就能避免对外置处理器的需要,从而降低整个系统的成本、复杂性、空间和功耗。

图5 – 现代汽车ECU中的FPGA应用,FPGA中集成了处理器(虚线)

评论