Xilinx FPGA的Fast Startup

高优先级分区的实现

本文引用地址:http://www.eepw.com.cn/article/125814.htm为了得到尽可能小的高优先级分区的部分比特流,设计中有一些一般性问题需要考虑。首先,该分区必须只能包含此类组件:或者是时序关键组件,或者是系统需要这些组件来执行低优先级部分(如ICAP)的部分重配置。得到小规模初始部分比特流的关键是使用尽可能小的区域实现高优先级分区。也就是说,您必须将这个分区局限在FPGA中的一个适当区域中。

为了在FPGA中找到理想的物理位置,这个区域应该提供该设计需要的适当数量的资源。访问该区域以外的资源也是可行的,但我们不鼓励这么做——尽管对于I/O引脚来说,

这样做一般是无法避免的。在寻找适当区域时,还要牢记的是这个FPGA区域有可能会妨碍FPGA设计中非时序关键部分的资源。

当您已经对FPGA进行分区,且已经找到了这些分区的适当区域之后,下一步就是使用一个空的(黑盒子)低优先级分区实现高优先级分区。得到的比特流含有很多针对未使用资源的配置帧。您可以删除这些帧,以便得到针对初步配置高优先级分区的有效部分比特流。[4]

低优先级分区的实现

为了创建低优先级的部分比特流,首先,您要创建含有这两个分区(即高优先级分区和低优先级分区)的完整FPGA设计的实现。从以前的实现中导入高优先级分区,从而保证其实现方法与原来的实现方法相同。

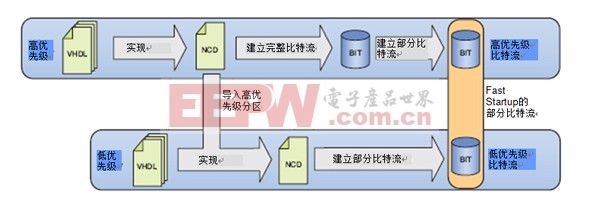

对于Virtex-6器件而言,部分重配置(PR)流程可用于所有上述的实现。这样,就会自动得到针对低优先级分区的部分比特流。由于Spartan-6器件 系列不支持PR流程,在实现针对Spartan-6设计的Fast Startup时,我们使用了针对差异化的部分重配置的BitGen选项,以获得低优先级分区的部分比特流。[5]图3给出了该工具流程的高层概览。

图3 – Fast Startup工具流程

实验与结果

为了在硬件中验证Fast Startup配置方法,我们的研究小组在一块Virtex-6 ML605板和一块Spartan-6 SP605板上实现了这种方法。

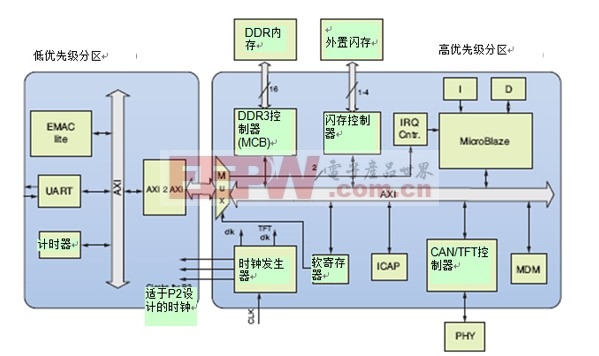

Virtex-6实现的应用背景源自视频领域。用户接通视频系统电源时,他们总是希望立刻就看到系统有所响应,而不用等待数秒。因此,在图4所示的系统中,一个配备了TFT控制器的高优先级子系统可以迅速点亮TFT屏幕。对于其他低优先级应用,即第二个设计提供了对以太网内核、UART和硬件计时器的控制和访问。

图4 – Virtex-6和Spartan-6演示(Virtex-6包括TFT模块,Spartan-6仅包括CAN模块)的基本框图

评论