基于JTAG边界扫描方式的重构控制器的设计

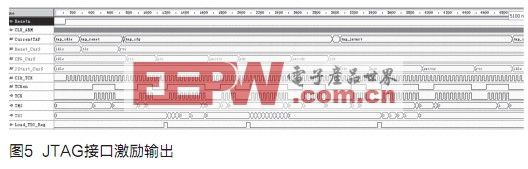

图5为各状态机个状态下接口输出波形,TCK、TMS、TDI时序和输出值满足JTAG扫描方式配置Virtex-4系列FPGA接口激励要求。

本文引用地址:http://www.eepw.com.cn/article/105941.htm

本系统ARM工作时钟为50MHz,TCK输出为25MHz,为便于观察,TAP_CFG部分状态机中SDR状态项实际由配置方案文件bit位数决定,仿真图有所压缩。

如果目标板FPGA是Virtex-4 XC4VLX25,其配置方案文件为995KB,整个配置过程大约所需时间327ms。

结语

本文介绍的重构控制器具有相对通用性,适用于对同一类FPGA芯片实现可编程器件在系统配置,使得硬件信息(可编程器件的配置信息)也可以象软件程序一样被动态调用或修改,从而动态的改变电路的结构和功能,对电路中出现的错误和故障进行实时动态重构,达到高可靠性的目的,有效节省逻辑资源,通过设计和仿真验证了此方法的可行性。

参考文献:

[1] Xilinx, Virtex-4 Configuration Guide, UG071 (v1.5). 2007

[2] IEEE Std.1149.1—2001, Test Access Port and Boundary Scan Architecture[S], IEEE, 2001

[3] Xilinx, Configuration and Readback of the Spartan-II and Spartan-IIE Families[D]. 2002

[4] 赵蕙. 边界扫描测试技术在远程实验系统中的应用研究[D]. 江苏大学, 2005

[5] ARM. ARM9TDMI Technical Reference Manual[EB/OL]. 2008

评论