基于JTAG边界扫描方式的重构控制器的设计

仲裁与时序控制模块

本文引用地址:http://www.eepw.com.cn/article/105941.htm仲裁与时序控制模块主要完成对重构控制器内部各模块的仲裁与时序控制。协调各模块之间的数据流向。其具体的功能包括提供内部各模块所需的时钟信号,并进行相应的时序控制;以及对内部数据流的切换控制。

TCK,TMS,TDI,TDO产生模块

TCK: JTAG配置时钟输入,所有基于JTAG的操作都必须同步于JTAG时钟信号TCK。关键时序关系是:TMS和TDI采样于TCK的上升边沿,一个新的 TDO值将于TCK下降边沿后出现,因此一般情况下JTAG的时钟不会太高。

TMS:模式选择,控制JTAG状态转移,同步时钟TCK上升沿时刻TMS的状态决定状态转移过程。

TDI :配置数据输入,配置数据在TCK的上升沿采样进入数据移位寄存器(SDR);

TDO:配置数据输出,在TCK的下降沿从移位寄存器移出,输出数据与输入到TDI的数据应不出现倒置。

目标板

目标板上被重构的FPGA由支持重构的Xilinx公司的VIRTEX-4系列FPGA来实现,以菊花链方式串联,支持JTAG边界扫描模式配置。

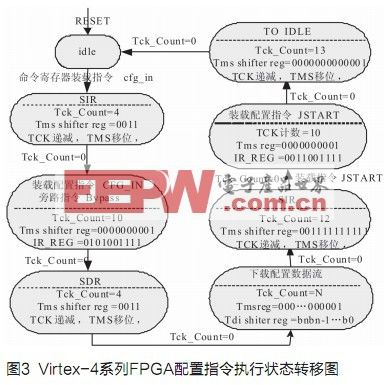

TAP控制器是16个状态的有限状态机,主要为JTAG接口提供控制逻辑。主要有四大状态:复位(RESET),空闲(idle),数据寄存器移位(SDR)和指令寄存器移位(SIR)状态, 在TCK,TMS的控制下,根据输入的配置指令实现状态的转移。Xlinx公司Virtex4系列 FPGA器件的边界扫描指令集中有三条专用于配置的边界扫描指令:CFG_IN、BYPASS和JSTART(10个bit位)。其中CFG_IN的代码:0101001111;BYPASS的代码:1111111111;JSTART的代码:0011001111。执行CFG_IN指令可以访问器件内部的配置总线,通过串行移入配置文件中的命令和数据执行对内部配置寄存器的读写,从而完成对FPGA的配置。BYPASS指令在对多个目标器件配置时可以旁路不需要重配置的器件。JSTART指令使用TCK时钟触发启动时序,使FPGA完成从配置状态到操作状态的转换,激活FPGA。图3为可重构控制器模拟TAP状态机配置指令执行的状态转移图。

评论