串行RapidIO在WiMAX基站系统中的应用

引言

本文引用地址:https://www.eepw.com.cn/article/101030.htm随着以TD-SCDMA、WCDMA为代表的3G移动通信全面进入商用部署,LTE标准基本完成,华为、爱立信成功实现LTE标准的现场演示,以IEEE802.16(WiMAX) 为标准的下一代移动通信技术、标准与系统的研发也已经开始。

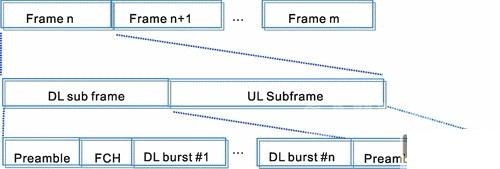

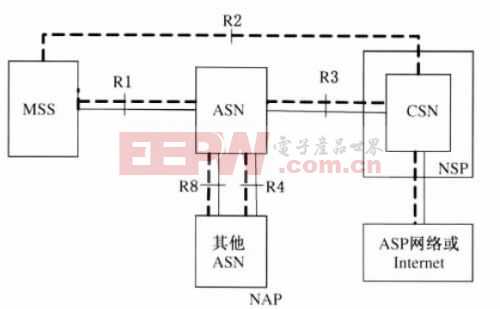

WiMAX(微波存取全球互通技术)和传统的TD-SCDMA、WCDMA和CDMA2000几个3G标准相比,WiMAX的最大传输半径达到了50公里上下,接近前者的两倍。而在传输速度上,WiMAX也让其他3G标准望尘莫及。在10公里范围内,WiMAX网络的速率可以达到 75Mbit/s。另外,WiMAX等无线通信系统要支持大量的宽带用户和极高的空中接口速率,使用MIMO、OFDM等复杂的通信信号处理算法,具有动态可重配置、计算资源动态调度能功能,对基站的计算处理和互连提出了极高的要求。这种高性能的无线通信系统在实现上有很大困难和挑战。典型的无线基站系统由CPU、DSP和FPGA构成。随着CPU、DSP和FPGA等处理器的性能得到较大提升,提高连接这些高性能器件的总线性能成为提升系统性能的关键。本文提出的基于串行RapidIO的无线基站系统解决了这一问题,该系统能够实现10Gbit/s的传输速度,适用WiMAX等新型的无线基站系统。

处理器选择

系统的实时处理能力主要取决于单个处理器的计算能力、存储结构配置和互连拓扑结构。现在应用到嵌入式系统的主流处理器是GPP/RISC、DSP 和FPGA。为了选择最佳处理器,需要从计算能力、易编程性、功耗、有效带宽和完整定义的接口等因素综合考虑。因此笔者选用以MPC8548、TMS320C6455为主处理器和Xilinx FPGA V5LX110为从处理器的系统架构。

MPC8548处理器使用e500v2内核,最高速率1.5GHz,集成L1/L2两级缓存,并集成了串行RapidIO和PCI Express高速互连接口,支持4x串行RapidIO。适用于传输千兆以上赫兹的通讯处理性能和高度集成和高速连接的高级功能。

TMS320C6455 是TI公司的一款具有高计算速度、低功耗的芯片。C6455的处理速度为9600MIPS。考虑到接口的实用性和带宽,C6455集成了一个4通道串行RapidIO(SRIO),此接口具有25Gbit/s的吞吐量。TMS320CC6455 的外围总线还包括:两个多路缓冲串口总线(McBSPs), 一个10/100/1000M以太网媒体访问控制器(EMAC),一个无缝外部存储器接口(64bit EMIFA),一个32 位DDR2 SDRAM接口等。丰富的外围总线使得基于C6455的设计灵活,支持强大的存储容量和高速的数据传送,适用于3G、WiMAX等基站系统设计。

串行RapidIO特性

基于TMS320C645x的RapidIO接口叫做SRIO(串行RapidIO)。SRIO有以下特点:引脚少;功耗低;SRIO协议栈简单,软件开销很小;数据宽度和速度可调具备DMA和消息传递功能;支持复杂可调整的拓扑结构;支持多点传送;可靠性高,可提供服务质量保证。

SRIO以上特点在实时信号处理系统中具有很大的应用前景。SRIO支持1x和4x模式。1x模式支持一个通道,运行速率有1.125Gbaud、2.5Gbaud、3.125Gbaud。4x模式支持4通道SRIO链路可以提供 10Gbit/s 的流量,且保证数据完整性。因为SRIO包处理是通过硬件实现的,这就意味着可大幅削减 I/O 处理方面的额外开销,降低延迟并增加系统带宽。但与多数总线接口不同,SRIO接口的引脚数较少,带宽在链路为3.125baud的基础上可继续扩展。

串行RapidIO 协议是一个点对点的包交换协议,由包和控制符号组成。SRIO有物理层、运输层和逻辑层3层结构。逻辑层定义总体的协议和分组格式;运输层为RapidIO 数据包提供了路由和寻址的功能;物理层负责描述器件的接口规范。结构的层次划分保证了任意层增加新的事务类型无需改变其他层规范,有助于设计的灵活性和更好的前后兼容性。图1说明了SRIO协议的分层机构。

评论