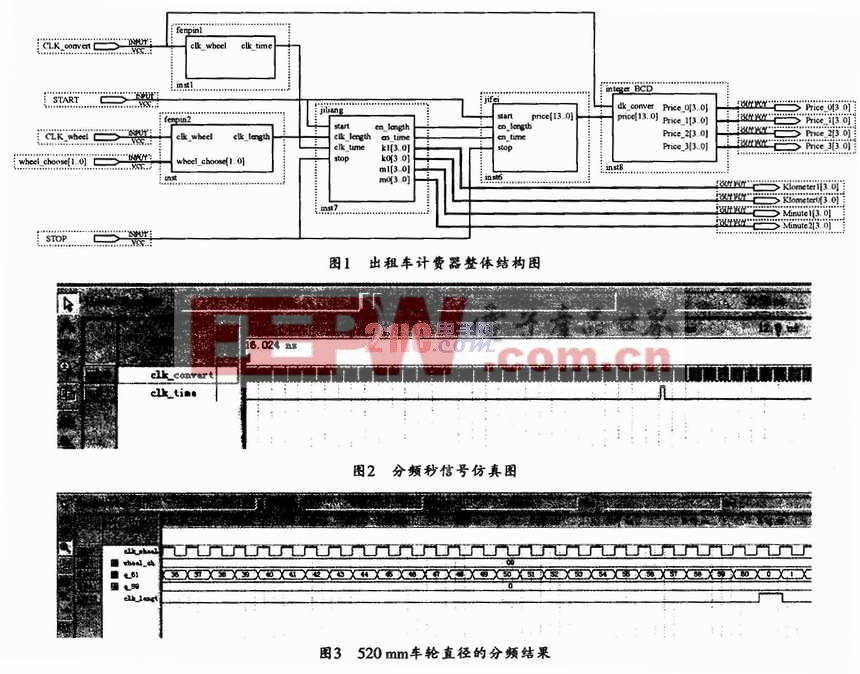

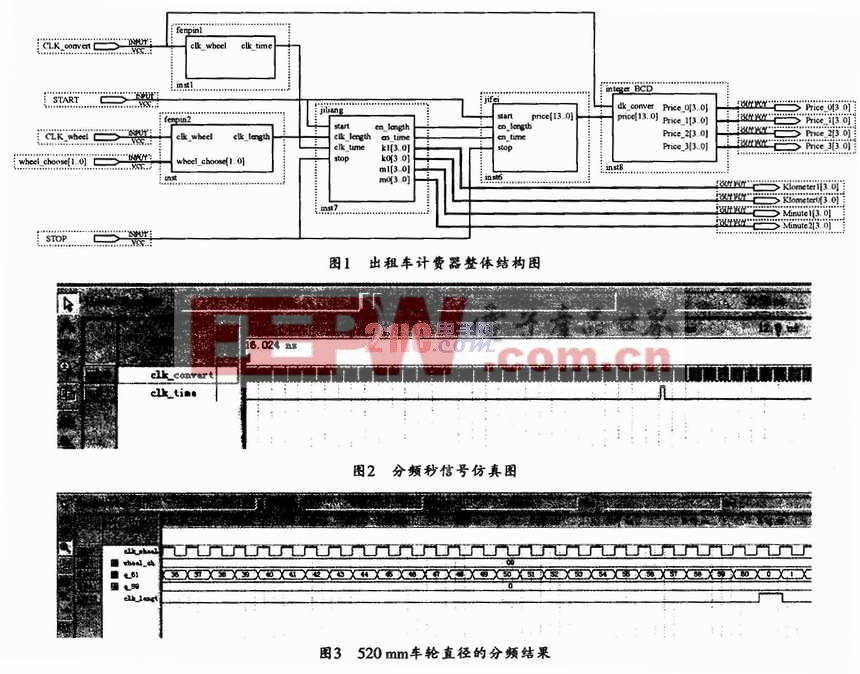

- 摘要:以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(VHDL)为主要表达方式,以QuartusⅡ开发软件和GW48EDA开发系统为设计工具,给出了一种出租车计费器的工作原理和软硬件实现方法。同时对该出租车计费器进

- 关键字:

FPGA

- “如今,FPGA(现场可编程门阵列)可以自如地协助半导体企业和系统设计企业将创意和产品快速得以实现,因此,在加速这些企业自主创新进程中,FPGA起着越来越重要的作用。”在日前于西安举行的2010年(第二届)中国FPGA产业发展论坛上,中国半导体行业协会秘书长陈贤向与会听众强调了FPGA在中国半导体行业自主创新历程中的重要贡献。来自国内外数十家企业、高等院校和科研机构的200多名代表参加了本次论坛,“可编程技术加速中国科技创新”正是此次论坛的主题。

- 关键字:

FPGA 半导体

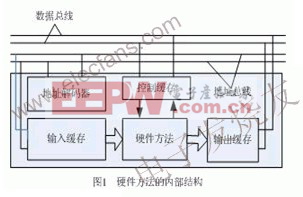

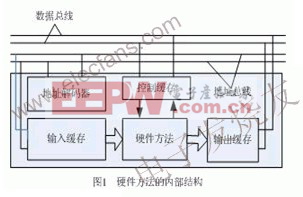

- 0引言远程通信系统和远程监控系统对信号传输有两方面的要求:一方面要求接口灵活且有较高的数据传...

- 关键字:

高速通信系统 FPGA

- 现了基于FPGA硬件及VHDL语言设计的LED点阵汉字滚动显示,可通过按键选择,控制其滚动方式:左移或者右移及上移或者下移等。阐述了LED点阵显示汉字的原理,给出了点阵汉字滚动显示控制器的原理图、部分VHDL源程序及时序仿真图并进行了详细的分析,提出了系统扩展成实现16×16点阵汉字滚动的改动思路。

- 关键字:

FPGA LED 汉字 滚动显示

- 针对某机载三轴运动平台的高精度伺服控制要求,设计了基于FPGA的伺服控制器。重点对硬件中的控制模块、驱动模块、通信模块和软件中的中断、复位、A/D转换等子程序进行了设计与实现。尤其是在驱动模块设计中,详细探讨了力矩电机的反馈环节参数给定模式。通过后续的仿真测试,验证了该三轴伺服控制器的有效性。

- 关键字:

FPGA 伺服 制器设计

- 球可编程平台领导厂商赛灵思公司与Vanguard Software Solutions 公司 (VSofts) 在 IBC2010 大会上联合演示了 VSofts H.264/AVC-I IP 核的强大功能:能实现超低延时,且其现场可编程门阵列 (FPGA) 实施方案不仅符合国际电信联盟 (ITU) 和 Panasonic AVC-Intra 标准,而且还支持业界标准的编解码器,能在实时视频广播应用中确保源视频到编码视频的最小延迟。

VSofts 市场营销副总裁 Felix Nemirovsky

- 关键字:

赛灵思 FPGA IP核

- 美国国家仪器有限公司(National Instruments,简称NI)近日发布NI 9157和NI 9159 MXI-Express RIO机箱,以及NI 9148以太网RIO机箱,这三款新产品在现有的NI 9144 EtherCAT机箱基础上,进一步扩展了NI基于各种总线的高通道数扩展机箱系列产品。利用NI可重配置I/O(RIO)技术,这些机箱将基于现场可编程门阵列(FPGA)的硬件和C系列I/O应用到了需要数百甚至数千通道数的应用。每一个扩展机箱含有一个可用NI LabVIEW FPGA模块编

- 关键字:

NI FPGA LabVIEW

- 针对DDS频率转换时间短,分辨率高等优点,提出了基于FPGA芯片设计DDS系统的方案。该方案利用A1tera公司的QuartusⅡ开发软件,完成DDS核心部分即相位累加器和ROM查找表的设计,可得到相位连续、频率可变的信号,并通过单片机配置FPGA的E2PROM完成对DDS硬件的下载,最后完成每个模块与系统的时序仿真。经过电路设计和模块仿真,验证了设计的正确性。由于FPGA的可编程性,使得修改和优化DDS的功能非常快捷。

- 关键字:

FPGA DDS

- 爱特公司(Actel CorporaTIon) 宣布其多种FPGA产品现可搭配使用加密内核,对抗差分功率分析(differential Power analysis, DPA)攻击。采用SmartFusion、Fusion、ProASIC3和 IGLOO的设计人员现可通过使用IP Cores公司(IP Cores, Inc.)的AES、GCM或ECC IP内核,保护其密钥不受DPA攻击。IP Cores是专业提供主要用于安全和加密领域的半导体用IP内核的供应商,而这些内核则是首次商业化地用于FPGA的

- 关键字:

Actel FPGA

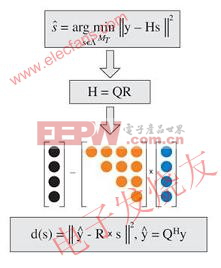

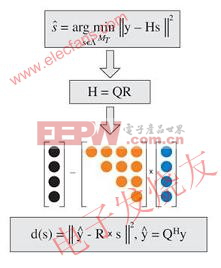

- 空分复用 (SDM) MIMO 处理可显著提高频谱效率,进而大幅增加无线通信系统的容量。空分复用 MIMO 通信系统作为一种能够大幅提升无线系统容量和连接可靠性的手段,近来吸引了人们的广泛关注。 MIMO 无线系统最

- 关键字:

系统 应用 FPGA 实现 通信 MIMO 检测 空分 复用 球形

- 基于Java的FPGA可编程嵌入式系统, 传统的嵌入式产品只能实现某种特定的功能,不能满足用户可变的丰富多彩的应用需求。为解决这个问题,本文设计并实现了一种使用Java作为软件平台的基于FPGA的可编程嵌入式系统,以实现系统对多种本地应用和网络的

- 关键字:

嵌入式 系统 可编程 FPGA Java 基于

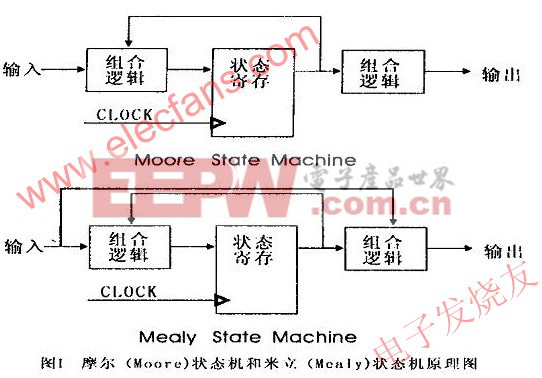

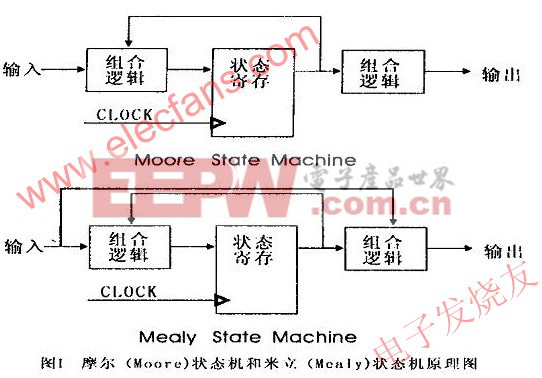

- FPGA/CPLD状态机的稳定性设计, 随着大规模和超大规模FPGA/CPLD器件的诞生和发展,以HDL(硬件描述语言)为工具、FPGA/CPLD器件为载体的EDA技术的应用越来越广泛.从小型电子系统到大规模SOC(Systemonachip)设计,已经无处不在.在FPGA/CPLD设计中,状

- 关键字:

设计 稳定性 状态 FPGA/CPLD

spartan.fpga介绍

您好,目前还没有人创建词条spartan.fpga!

欢迎您创建该词条,阐述对spartan.fpga的理解,并与今后在此搜索spartan.fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473