- 随着宽带Internet的快速发展和电子设备计算能力的迅速提高,在Internet上实时传输高清晰度视频信息成为可能,...

- 关键字:

DSP FPGA 视频编码器

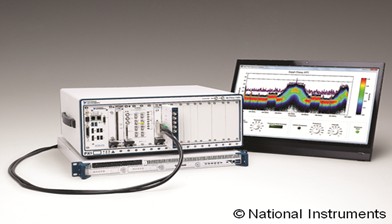

- 美国国家仪器有限公司(National Instruments, 简称NI)- NIWeek - 近日发布了数款基于NI LabVIEW可重配置I/O(RIO)架构的新产品,为用户提供灵活性,帮助他们应对现代自动化测试系统的挑战并降低总测试成本。

- 关键字:

NI LabVIEW FPGA

- 由于ASIC解决方案NRE成本高,产品开发周期较长,在支持各种不同无线标准升级上灵活性不足。而FPGA的功耗对于高 ...

- 关键字:

多核DSP ASIC FPGA

- 在新的半导体制造工艺中,FPGA通常是最先被采用、验证和优化该工艺的器件之一。Altera公司资深副总裁,首席技术 ...

- 关键字:

FPGA 系统架构

- 据CEVA公司市场拓展副总裁Eran Briman介绍,虽然现在DSP和FPGA有相互渗透的趋势,但是DSP在成本方面还是具备比较大的优势,尤其消费电子产品对成本更加敏感,所以DSP在消费电子领域还有比较大的发展空间。但是这一市场发展速度很快,Eran Briman表示,只有针对专门市场推出专门的DSP应用才是未来DSP的发展之道。

- 关键字:

CEVA DSP FPGA 201309

- Altera公司 (NASDAQ: ALTR)和Micron技术有限公司(NASDAQ: MU) (“Micron”)日前宣布,双方联合成功展示了Altera Stratix® V FPGA和Micron混合内存立方 (Hybrid Memory Cube, 简称HMC)的互操作性。采用这一成功的技术,系统设计人员能够在下一代通信和高性能计算设计中充分发挥FPGA和SoC的HMC优势。

- 关键字:

Altera Micron FPGA HMC FPGA

- 介绍了一种以FPGA可编程逻辑器件为设计平台的、采用大屏幕全彩led显示屏进行全彩灰度图像显示的扫描控制...

- 关键字:

FPGA led显示屏

- 薪资往往是绝大多数职场人选择职业的首要条件,为了帮助我们的读者了解FPGA工程师薪酬水平, EEPW统计了大中华区FPGA工程师薪酬TOP15公司(表1),为读者的薪酬及职业规划提供参考与借鉴。

- 关键字:

FPGA Xilinx Altera IC设计

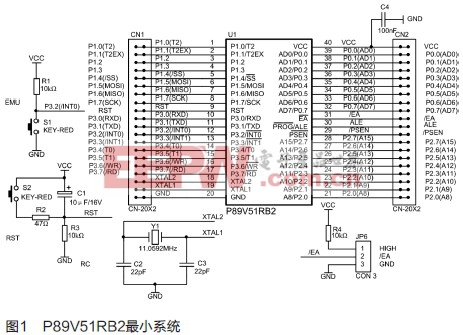

- 摘要:随着人们生活水平的不断提高,单片机控制成为人们追求的目标之一。要为现代人工作、科研、生活等提供更好、更方便的设施需要从数字单片机技术入手,朝着数字化控制、智能控制发展。本设计P89V51RB2单片机实验箱与传统的实验箱相比,使用方便,所包含的实验电路全面和实用。

- 关键字:

单片机 实验箱 控制 FPGA LED 201309

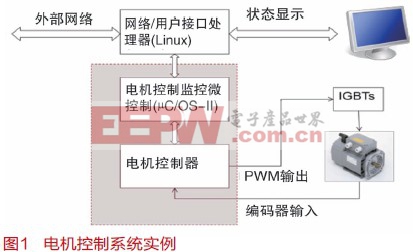

- 摘要:随着FPGA在嵌入式领域的快速发展和网络技术的日益成熟,基于FPGA的网络开发成为嵌入式系统研究的重要分支。本文系统地研究了FPGA网络通信,并成功运用Xilinx开发平台EDK构建一个基于总线AXI4的嵌入式网络服务系统。

- 关键字:

FPGA 总线AXI4 lwip 以太网 实时控制 201309

- 摘要:随着ARM Cortex-A9多处理器和FPGA SoC的推出,可把现有的分立微控制器和数字逻辑功能集成到一个多核器件中。这减小了功耗和体积,而主要难点之一是在一个器件中同时实现安全关键和非安全关键软件单元。

- 关键字:

ARM TrustZone 安全 FPGA HPS 201309

- 无线设备的数量、通信标准的多样性,以及调制方案的复杂度,每一年都在不断增加。而随着每一代新技术的诞生,由于使用传统技术测试无线设备,需要大量更复杂的测试设备,其成本也在不断提高。

- 关键字:

NI LabVIEW FPGA 射频仪器 CPU

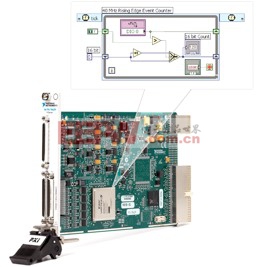

- 研究的是基于FPGA的电机测速系统设计。该设计以有源晶振来产生时基信号,利用欧姆龙光电编码器E682-CWZ6C360P/R将转速信号转变为频率信号,采用数码管动态显示来显示测量所得的数值。FPGA模块的编写是基于Altera公司的Quartus II软件进行编写的,采用的芯片型号为EP2C5T144C8N。FPGA模块是利用VHDL语言进行编写,利用Quartus II软件自带的仿真软件进行仿真,通过观察仿真波形来验证模块是否正确。本设计可以实现小数值的方波频率测量和电机转速测量。

- 关键字:

FPGA 电机测速 系统设计

- 随着数字技术的发展,数字产品的普及,各种数字电视工作人员专用测试工具不断被开发。针对码流播放器的市场需要的目的,采用基于FPGA的系统架构的方法,结合硬件及软件设计等方面内容,文中详细介绍了一个包含码流录制、码流播放、码流分析等多种功能的ASI/SDI码流播放器的设计与实现的过程。

- 关键字:

FPGA ASI SDI 码流播放器

spartan.fpga介绍

您好,目前还没有人创建词条spartan.fpga!

欢迎您创建该词条,阐述对spartan.fpga的理解,并与今后在此搜索spartan.fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473