- 基于FPGA和DDS的信号源设计,1 引言

直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率

- 关键字:

设计 信号源 DDS FPGA 基于 FPGA,DDS,Verilog HDL

- 作为一个负责FPGA 企业市场营销团队工作的人,我不得不说,由于在工艺技术方面的显著成就以及硅芯片设计领域的独创性,FPGA 正不断实现其支持片上系统设计的承诺。随着每一代新产品的推出,FPGA 在系统中具有越来来越多的功能,可作为协处理器、DSP 引擎以及通信平台等,在某些应用领域甚至还可用作完整的片上系统。

因此,在摩尔定律的作用下,FPGA 产业的门数量不断增加,性能与专门功能逐渐加强,使得 FPGA 在电子系统领域能够取代此前只有 ASIC 和 ASSP 才能发挥的作用。不过,说到底,F

- 关键字:

xilinx FPGA VHDL Verilog

- 直接数字频率合成技术(Direct Digital Synthesize,DDS)是继直接频率合成技术和锁相式频率合成技术之后的第三代频率合成技术。它采用全数字技术,并从相位角度出发进行频率合成。随着微电子技术和数字集成电路的飞速

- 关键字:

Verilog HDL DDS 仿真

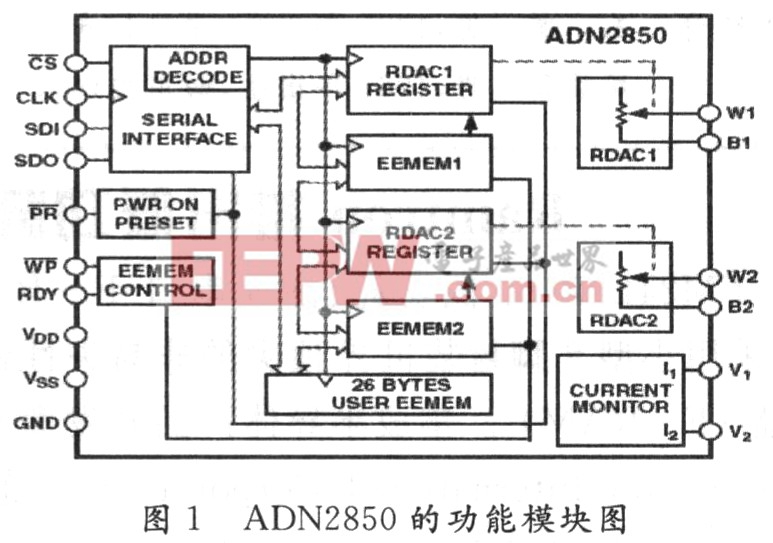

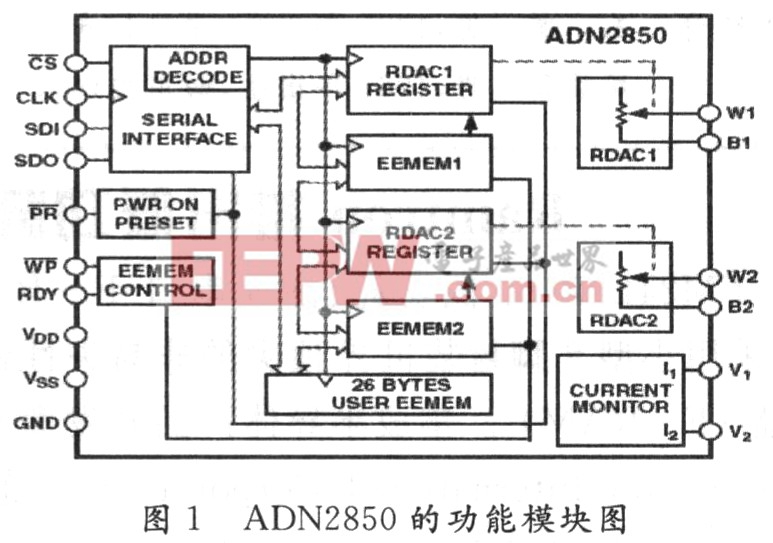

- 摘要:数字电位器由于可调精度高,更稳定,定位更准确,操作更方便,数据可长期保存和随时刷新等优点,在某些场合具有模拟电位器不可比拟的优势。论述对数字电位器ADN2850的一种方便的控制方法,通过计算机上的串口直

- 关键字:

串口 控制 ADN2850 数字电位器 Verilog HDL 基于

- 在工信部电子信息司的指导下,工业和信息化部软件与集成电路促进中心(CSIP )联合集成电路IP核标准工作组,现面向全国集成电路设计企业工程师、科研院所及高校师生,举办2009年“首届中国开源IP核标准化设计竞赛”,竞赛报名工作已于6月3日启动。报名及详情咨询可登录竞赛官方网站 http://www.ipmall.org.cn了解。据悉本次竞赛获奖者可分别获得现金1万元、5千元等奖励,针对学生参赛者有机会获得到IBM中国芯片设计中心实习的机会!

参赛者可以个人或团队(不高于

- 关键字:

CSIP VHDL Verilog

- 0 引 言

除法器是电子技术领域的基础模块,在电子电路设计中得到广泛应用。目前,实现除法器的方法有硬件实现和软件实现两种方法。硬件实现的方法主要是以硬件的消耗为代价,从而有实现速度快的特点。用硬件的方

- 关键字:

Verilog 计算 精度可调 整数除法器

- 0 引 言

USB(通用串行总线)是英特尔、微软、IBM、康柏等公司1994年联合制定的一种通用串行总线规范,它具有数据传输速度快,成本低,可靠性高,支持即插即用和热插拔等优点,迅速得到广泛应用。

在高速的数

- 关键字:

Verilog FPGA USB 高速接口

- 针对机器人伺服控制系统高速度、高精度的要求,介绍一种全数字化的基于神经网络控制的直流电机速度伺服控制系统的设计方案。速度控制器采用BP网络参数辨识自适应控制,并将其在FPGA进行硬件实现;同时用Nios II软核处理器作为上位机,构成一个完整的速度伺服控制器的片上可编程系统(SOPC)。实验结果表明,该控制系统具有较高的控制精度、较好的稳定性和灵活性。

- 关键字:

SOPC 系统 控制器 速度 神经网络 电机 基于 神经网络 伺服控制 现场可编程门阵列 Verilog HDL

- 1 引 言

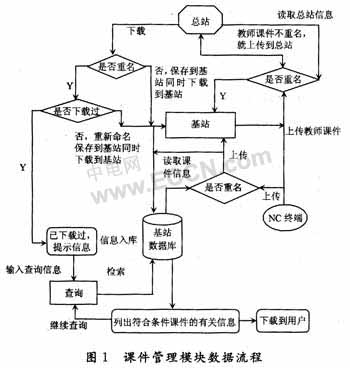

Linux最早是由芬兰大学生Linus Torvalds于1991年开发的,其借鉴Unix系统当时近30年的技术积累,并且综合主流Unix系统的优点。他遵照Unix标准设计的个人计算机和工作站上的Unix类操作系统。他具有用户希望的任何一个成熟的现代Unix系统的一切特点,包括真正的多任务功能、多用户、虚拟内存、共享库、高级内存管理等。

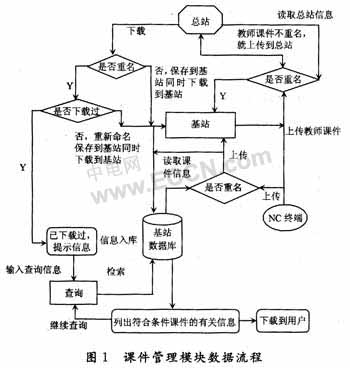

“基于Linux的网络多媒体教学资源建设关键技术与应用研究”课题主要是依托贵州省高校千兆城域网基础与相对技术优势:一是扩建

- 关键字:

Linux NC

- 引言

在轴承生产行业中,轴承振动噪声的峰值检测是一项重要的指标。以往,该检测都是采用传统的模拟电路方法,很难做到1:1地捕捉和保持较窄的随机波形的最大正峰值。本文叙述了基于Verilog-HDL与高速A/D转换器相结合所实现的快速轴承噪声检测方法。

1 振动噪声电压峰值检测方案的确定

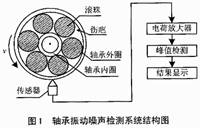

1.1 轴承振动噪声的产生及检测

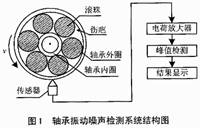

图1是轴承振动噪声电压峰值检测系统的示意图。由于加工设备、技术、环境等因素的影响,生产的轴承都程度不同地带有伤疤。图1中,假设某待测轴承有一处伤疤。由于伤痕的存在,轴

- 关键字:

Verilog 轴承 振动噪声 电压峰值检测

- 随着集成电路制造技术的迅速发展,SOC设计已经成为当今集成电路设计的发展方向。SO C设计的复杂性对集成电路设计的各个层次,特别是对系统级芯片设计层次,带来了新挑战,原有的HDL难以满足新的设计要求。

硬件设计领域有2种主要的设计语言:VHDL和Verilog HDL。而两种语言的标准不统一,导致软硬件设计工程师之间工作交流出现障碍,工作效率较低。因此,集成电路设计界一直在寻找一种能同时实现较高层次的软件和硬件描述的系统级设计语言。Synopsys公司与Coware公司针对各方对系统级设计语言的

- 关键字:

SOC SystemC 集成电路 VHDL Verilog HDL

- 在现代IC设计中,特别是在模块与外围芯片的通信设计中,多时钟域的情况不可避免。当数据从一个时钟域传递到另一个域,并且目标时钟域与源时钟域不相关时,这些域中的动作是不相关的,从而消除了同步操作的可能性,并使系统重复地进入亚稳定状态[1]。在有大量的数据需要进行跨时钟域传输且对数据传输速度要求比较高的场合,异步FIFO是一种简单、快捷的解决方案。

异步FIFO用一种时钟写入数据,而用另外一种时钟读出数据。读写指针的变化动作由不同的时钟产生。因此,对FIFO空或满的判断是跨时钟域的。如何根据异步的指针

- 关键字:

FIFO 异步 Verilog HDL IC 亚稳态

- 1.引言

随着集成电路复杂度越来越高,测试开销在电路和系统总开销中所占的比例不断上升,测试方法的研究显得非常突出。目前在测试源的划分上可以采用内建自测试或片外测试。内建自测试把测试源和被测电路都集成在芯片的内部,对于目前SOC级的芯片测试如果采用内建自测试则付出的硬件面积开销则是很大的,同时也增加了芯片设计的难度:因此片外测试便成为目前被普遍看好的方法。由于FPGA具有可重构的灵活性,利用FPGA来作为测试源实现片外测试就是一种非常有效的手段。

由于伪随机模式测试只需要有限个数的输入向量便

- 关键字:

嵌入式系统 单片机 FPGA 序列生成器 Verilog HDL MCU和嵌入式微处理器

nc-verilog介绍

您好,目前还没有人创建词条nc-verilog!

欢迎您创建该词条,阐述对nc-verilog的理解,并与今后在此搜索nc-verilog的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473