- 莱迪思半导体公司(NASDAQ: LSCC)与Helion今天宣布他们已经发布知识产权(IP)核用于视频安全和监控摄像机市场。针对LatticeXP2™、LatticeECP2M™和LatticeECP3™FPGA系列,Helion展示了其IONOS流水线型视频IP和Vesta评估平台。Helion Vesta评估平台是一个完全独立的平台,能够开发和实现针对摄像机系统的图像流水线技术,尤其是紧凑形式的视频安全应用,如网络IP和球型摄像机。

Helion的Ves

- 关键字:

Lattice 视频监控 视频安全 IP核

- IP(IntellectualPropcrty)就是常说的知识产权。美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC...

- 关键字:

IP核 晶闸管 EDA VHDL

- 在几年前如果有人将ARM和Intel相提并论,一定会被同行耻笑。Intel是一家年销售额过300亿美金,每年研发投入超过50亿美元,在全球拥有近10万员工的IT巨头,而ARM仅仅是一家“著名的小公司”,其销售额仅仅几个亿美金而已,在全球拥有不到2000名员工。但今天,当Intel要大力拓展嵌入式市场,极力宣传其处理器极其适用于嵌入式应用的时候,却遇到了一个绕不过的竞争对手,ARM。其实,Intel面对的绝不仅仅是一家ARM公司,它面对的是一个ARM公司营造起来的生态系统。

半

- 关键字:

Intel ARM IP核 生态价值

- 摘要: 重点阐述了USB接口IP核关键模块的设计和验证,用VerilogHDL对USBIP核协议RTL级代码编写,对USB协议的数据流、传输等进行了深入的分析,在Xilinx ISE软件平台上进行了FPGA综合,并在Xilinx FPGA开发板上调试成功

- 关键字:

FPGA USB IP核 接口

- 亮相IIC-China 2010,聚焦自主知识产权

Tensilica将于3月15-16日亮相上海IIC-China 2010(国际集成电路研讨会暨展览会)。针对金融危机对半导体产业的影响、半导体厂商在研发成本方面的问题以及领先的中国半导体厂商对于自主知识产权的孜孜追求,Tensilica 在本届展会上将着重展示其可配置处理器在帮助企业研发自主知识产权方面的卓越表现(展位号:8S35)。Tensilica亚太区总监黄启弘将在高峰论坛做出“Tensilica灵活配置的DSP,帮您实现自主知

- 关键字:

自主知识产权 Xtensa ConnX DSP IP核

- 1 引言 随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合为一个系统,提高了设计效率,加快了设计过程,缩短了产品上市时间。但是随着设

- 关键字:

BIST 编译码器 IP核 测试

- 设计基于FPGA的8段数码管动态显示IP核,介绍8段数码管内部结构及其驱动显示方式和IP核设计方法,给出8段数码管动态显示IP核的Verilog HDL程序源代码及其C语言驱动程序。此IP核可例化成1~8个共阴极(或共阳极)数码管控制器,能方便地控制1~8个数码管同时显示数字和小数点位。测试结果表明,该IP核工作可靠、稳定,可直接应用于电子设计中。

- 关键字:

FPGA 8段数码管 动态显示 IP核

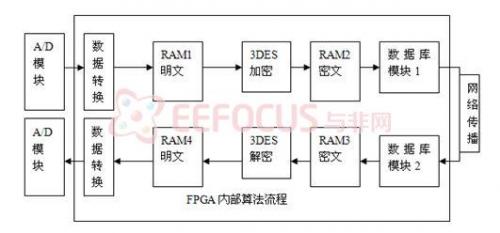

- 信息社会中,基于密码算法设计的安全芯片,能够为用户的敏感信息提供有效的机密性与完整性保护。信息化的不断深入使得人们对信息安全服务的需求呈现使用简单化、功能多样化、高度集成化等趋势。这要求安全芯片在

- 关键字:

安全芯片 IP核 密码算法 集成方法

- 引 言

SoC设计的快速发展是以IP核复用为基础的。IP核的复用极大地提高了SoC系统设计的开发效率,SoC 片上总线的选择是IP核间集成与互连的关键技术之一。目前片上总线的标准协议众多,如ARM公司提出的AMBA总线

- 关键字:

AMBA SOC 息线 IP核

- 随着电路复杂性的增加,越来越多的设计者开始采用拥有知识产权的、设计良好的功能模块来加快系统开发。因此,需要相应的技术手段保护这些功能模块不被非法复制、篡改或窃取。针对FPGA开发中的知识产权保护问题,提出一种结合EDA软件和FPGA的IP(Intellectual Proterty)核保护方法,有效的防止IP核被窃取,以及防止最终在FPGA上实现设计的非法复制。

- 关键字:

FPGA EDA 软件 IP核

- 发展国内硅知识产权,首先要重视高端通用IP核研发、验证与评估。

SoC实现的重要途径是复用高质量的成熟IP。而IP设计和验证是高质量IP开发流程中两个不可或缺的部分。应该看到,由于国内IP供应商在产品和技术上不够成熟,国外有成熟产品的IP供应商难以提供全面的本地技术支持等因素,SoC设计者和IP开发者都提出IP核评测的迫切需求。尤其是随着工艺的不断进步及IP复杂度的不断提高,IP设计和验证也面临着越来越多的挑战。所以,根据SoC/IP系统的特点,提高验证的效率和验证的可重用性,创建新的验证解决方

- 关键字:

IC设计 SoC IP核 集成电路

ip核介绍

IP核概述

IP核则是一段具有特定电路功能的硬件描述语言程序,该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片。利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP核的市场活动还不规范,但是仍有许多集成电路设计公司从事IP核的设计、开发和营销工作。IP核有两种,与工艺无关的VHDL程序称为软核;具有特定电路 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473