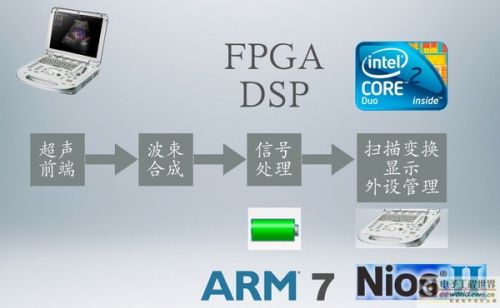

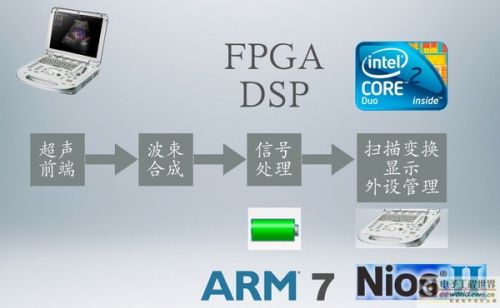

- “迈瑞对于处理器平台的选择有两个看似矛盾的原则:‘多’和‘少’。其中‘多’是指多样性,我们知道无论是DSP、ARM、X86还是FPGA、GPU,每个平台都有各自的优点和缺陷,因此在设计产品时就可以根据他们的特点进行选择和搭配,处理器平台的多样性以及合理的搭配可以使产品更具有竞争力。”在日前举办的第三届中国国际医疗电子技术大会(CMET2010)上,深圳迈瑞生物医疗电子硬件技术委员会执行主任、系统工程师姚力与

- 关键字:

FPGA ARM

- 系统概述

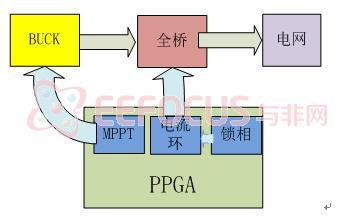

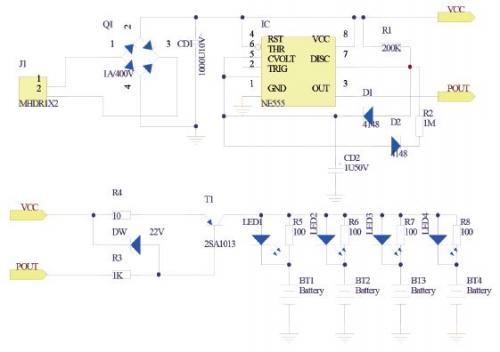

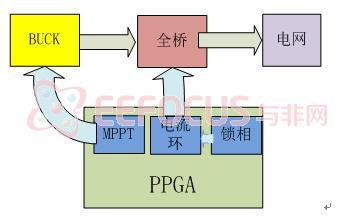

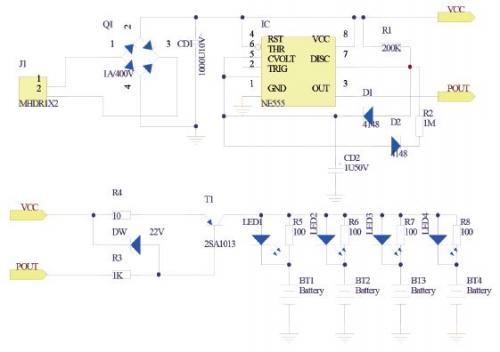

新能源发电成为21世纪解决能源危机的必经出路,光伏发电、风电、核电等新能源发电是目前新能源发电研究的几大方向。这几种新能源各有各的特点,我们选择了最靠近我们的光伏发电作为研究出发点。

目前光伏发电并网技术的研究愈加深入成熟,而关于光伏发电技术的具体应用环节还是有着许多发挥余地。光伏发电的优点是清洁安全、分布相对较为均匀、可持续利用。同时光伏发电也存在自己的问题,其中一个很重要的问题是光伏发电需要做的是收集辐射到地表的太阳能,这个环节需要占用大量的空间,这个问题使光伏发电的应用有着

- 关键字:

FPGA 逆变器

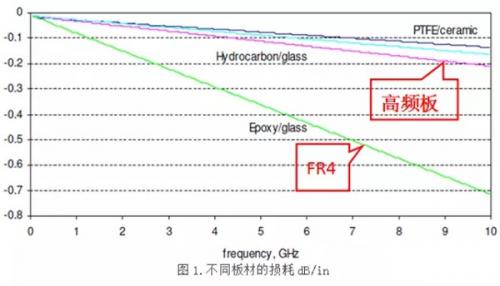

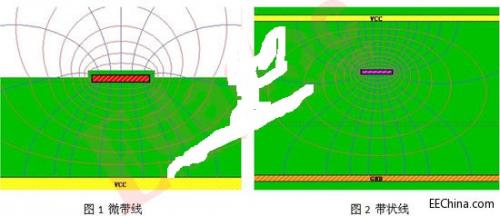

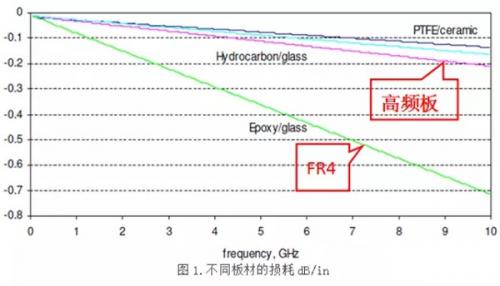

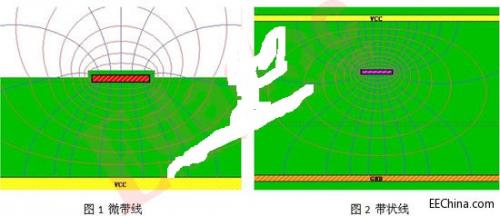

- 随着微处理器和信号转换传输器件运行速度提升,数字电路的运行速度也达到一个更高层次:100Gbps。使用通用的PCB板材将不能达到高速信号要求,电路板的选材将会决定产品的性能。

选 择PCB板材必须在满足设计需求、可量产性、成本中间取得平衡点。简单而言,设计需求包含电气和结构可靠性这两部分。通常在设计非常高速的PCB板子(大 于GHz的频率)时这板材问题会比较重要。例如,现在常用的FR-4材质,在几个GHz的频率时的介质损Df(Dielectricloss)会很大,可 能就不适用。

- 关键字:

PCB 高频

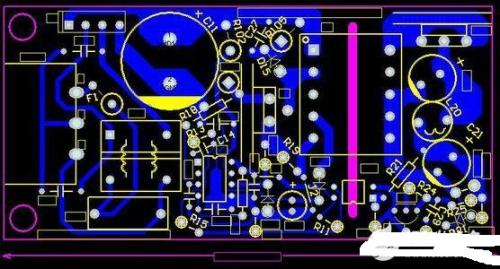

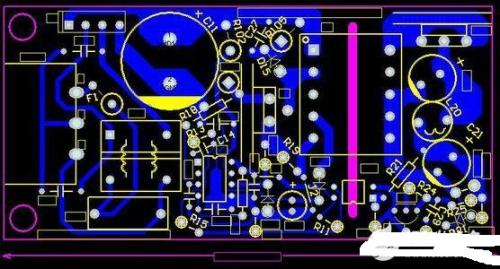

- 原理图设计软件:会ORCAD就可以了,支持的Netlist超多,基本是业界标准。

PCB Layout软件

1.Protel,现在推Altium Designer.国内低端设计的主流,国外基本没人用。简单易学,适合初学者,容易上手;占用系统资源较多,对电脑配置要求较高。在国内使用protel的人还是有相当的市场的,毕竟中小公司硬件电路设计还是低端的居多,不过建议各位尽早接触学习别的功能更优秀的软件,不要总在低层次徘徊,对薪水不是很友好啊,呵呵。

2、pads PADS软件用的人也是相

- 关键字:

pcb ORCAD

- 1、Abrasives磨料,刷材

对板面进行清洁前处理而磨刷铜面所用到的各种物料,如聚合物不织布,或不织布掺加金刚砂,或其砂料之各型免材,以及浮石粉(Pumice Slurry)等均称之为Abrasives.不过这种掺和包夹砂质的刷材,其粉体经常会着床在铜面上,进而造成后续光阻层或电镀层之附着力与焊锡性问题。附图即为掺和有砂粒的刷材纤维其之示意情形。

2、Air Knife风刀

在各种制程联机机组的出口处,常装有高温高压空气的刀口以吹出风刀,可以快速吹干板面,以方便取携及减少氧化的机

- 关键字:

PCB

- 手术很重要,术后恢复也必不可少!各种PCB布线完成之后,就ok了吗?很显然,不是!PCB布线后检查工作也很必须,那么如何对PCB设计中布线进行检查,为后来的PCB设计、电路设计铺好“路”呢?本文会从PCB设计中的各种特性来教你如何完成PCB布线后的检查工作,做好最后的把关工作!

在讲解PCB布线完成后的检查工作之前,先为大家介绍三种PCB的特殊走线技巧。将从直角走线,差分走线,蛇形线三个方面来阐述PCB LAYOUT的走线:

一、直角走线(三个方面)

直角走线

- 关键字:

PCB 走线

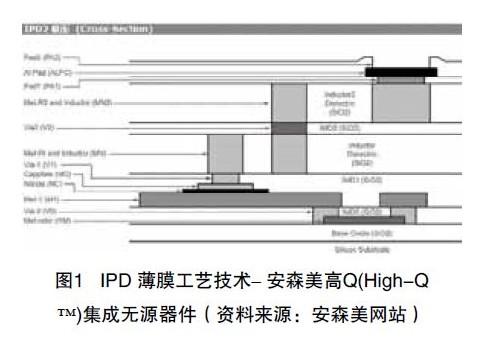

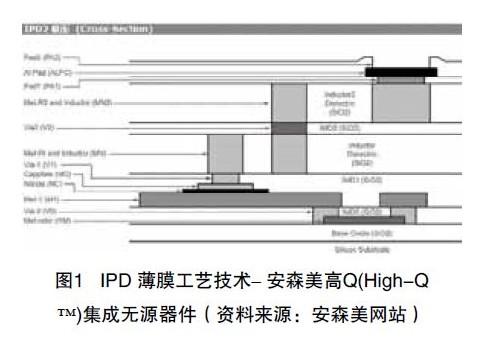

- 集成无源元件技术可以集成多种电子功能,具有小型化和提高系统性能的优势,以取代体积庞大的分立无源元件。文章主要介绍了集成无源元件技术的发展情况,以及采用IPD薄膜技术实现电容。电阻和电感的加工,并探讨了IPD对PCB技术发展的影响。

1引言

随着电子技术的发展,半导体从微米制程进入纳米制成后,主动式电子元件的集成度随之大幅提升,相对搭配主动元件的无源元件需求量更是大幅增长。电子产品的市场发展趋势为轻薄短小,所以半导体制程能力的提升,使相同体积内的主动元件数大增,除了配套的无源元件数量大幅增加

- 关键字:

无源元件 PCB

- 信号在媒质中传播时,其传播速度受信号载体以及周围媒质属性决定。在PCB(印刷电路板)中信号的传输速度就与板材DK(介电常数),信号模式,信号线与信号线间耦合以及绕线方式等有关。随着PCB走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。本文基于仿真分析DK,串扰,过孔,蛇形绕线等因素对信号时延的影响。

1.引言

信号要能正常工作都必须满足一定的时序要求,随着信号速率升高,数字信号的发展经历了从共同步时钟到

- 关键字:

PCB DDR

- 探讨使用PROTEL设计软件实现高速电路印制电路板设计的过程中,需要注意的一些布局与布线方面的相关原则问题,提供一些实用的、经过验证的高速电路布局、布线技术,提高了高速电路板设计的可靠性与有效性。结果表明,该设计缩短了产品研发周期,增强市场竞争能力。

1问题的提出

随着电子系统设计复杂性和集成度的大规模提高,时钟速度和器件上升时间越来越快,高速电路设计成为设计过程的重要部分。在高速电路设计中,电路板线路上的电感与电容会使导线等效成为一条传输线。端接元件的布局不正确或高速信号的错误布线都会引

- 关键字:

PROTEL PCB

- 电子电路中,共阻抗干扰对电路的正常工作带来很大影响。在PCB电路设计中,尤其在高频电路的PCB设计中,必须防止地线的共阻抗所带来的影响。通过对共阻抗干扰形式的分析,详细介绍一点接地在电子电路中,特别是在高频电路中对共阻抗干扰的抑制作用,以及采用一点接地防止共阻抗应注意的问题。

同时对PCB板内地线布局的主要形式和要求进行了简要阐述。

0前言

在电子电路中,多数元器件都要通过地线形成回路,线设计合理与否,直接影响电路的工作。尽可能地降低由于地线设计不和理产生对信号传输的干扰。

在

- 关键字:

PCB 抗干扰

- 1 Protel软件简介

随着电子信息技术的飞速发展,手工设计电子产品的PCB(印制电路板)已不能适应电子技术发展的需要。我们必须借助计算机来完成PCB的设计工作,它不仅速度快,准确性高,并能极大的减轻工程技术人员的劳动强度。其中涉及的软件有许多种,Protel是其中比较经典的一种。

Protel是Altium公司推出的电路辅助设计系统,它是第一个将所有的设计工具集成于一身的板卡级设计系统,包括了原理图设计、PCB设计、电路仿真、PLD设计等。它最早的版本是TANGO软件包,后来发展为Pr

- 关键字:

PCB Protel

- 解决EMI问题的办法很多,现代的EMI抑制方法包括:利用EMI抑制涂层、选用合适的EMI抑制零配件和EMI仿真设计等。本文从最基本的PCB布板出发,讨论PCB分层堆叠在控制EMI辐射中的作用和设计技巧。

电源汇流排

在 IC的电源引脚附近合理地安置适当容量的电容,可使IC输出电压的跳变来得更快。然而,问题并非到此为止。由于电容呈有限频率响应的特性,这使得电容无法 在全频带上生成干净地驱动IC输出所需要的谐波功率。除此之外,电源汇流排上形成的瞬态电压在去耦路径的电感两端会形成电压降,这些瞬态

- 关键字:

PCB EMI

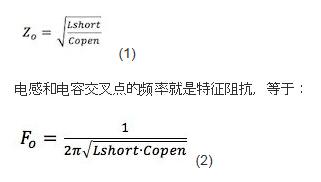

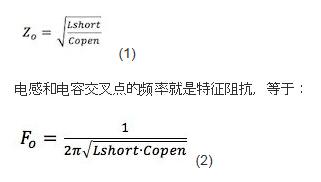

- 电源分配网络(PDN)的基本设计规则告诉我们,最好的性能源自一致的、与频率无关的(或平坦)的阻抗曲线。这是电源稳定性非常重要的一个理由,因为稳定性差的电源会导致阻抗峰值,进而劣化平坦的阻抗曲线,以及受电电路的性能。

由于没有阻抗路径是完全平坦的,所以我们需要做一些设计调整。本文旨在帮助你做出一些对系统性能影响最小的折衷。

源阻抗应该匹配传输线阻抗。

一般来说,这是S参数测量和所有射频设备的基本前提。源阻抗(最常见的是50Ω)连接到阻抗与源匹配的同轴电缆,负载也端接到相同的

- 关键字:

PCB PDN

- PCB(PrintedCircuitBoard),中文名称为印制电路板,又称印刷电路板、印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气连接的提供者。由于它是采用电子印刷术制作的,故被称为“印刷”电路板。

随着PCB尺寸要求越来越小,器件密度要求越来越高,PCB设计的难度也越来越大。如何实现PCB高的布通率以及缩短设计时间,在这笔者谈谈对PCB规划、布局和布线的设计技巧。

在开始布线之前应该对设计进行认真的分析以及对工具软件进行认真的设置,这会使

- 关键字:

PCB 布线

- PCB最佳设计方法:将PCB原理图传递给版图(layout)设计时需要考虑的六件事。本文中提到的所有例子都是用Multisim设计环境开发的,不过在使用不同的EDA工具时相同的概念同样适用。

初始原理图传递

通过网表文件将原理图传递到版图环境的过程中还会传递器件信息、网表、版图信息和初始的走线宽度设置。

下面是为版图设计阶段准备的一些推荐步骤:

1.将栅格和单位设置为合适的值。为了对元器件和走线实现更加精细的布局控制,可以将器件栅格、敷铜栅格、过孔栅格和SMD栅格设计为1mil

- 关键字:

PCB 原理图

fsp:fpga-pcb介绍

您好,目前还没有人创建词条fsp:fpga-pcb!

欢迎您创建该词条,阐述对fsp:fpga-pcb的理解,并与今后在此搜索fsp:fpga-pcb的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473