- Altera公司(Nasdaq: ALTR) 日前宣布,提供FPGA业界的第一款用于OpenCL™ 的软件开发套件(SDK) (开放计算语言) 的软件开发套件,它结合了FPGA强大的并行体系结构以及OpenCL并行编程模型。利用这一SDK,熟悉C语言的系统开发人员和编程人员能够迅速方便的在高级语言环境中开发高性能、高功效、基于FPGA的应用。

- 关键字:

Altera FPGA OpenCL

- 主要FPGA供应商已经开始销售集成了硬核处理器内核的低成本FPGA器件,SoC类FPGA器件最终会成为主流。为能够充分发挥所有重要FPGA的灵活性,这些器件提供了FPGA设计人员和软件工程师还不熟悉的新特性。设计人员需要考虑

- 关键字:

FPGA SoC

- 帧存是图形处理器与显示设备之间的数据通道,所有要显示的图形数据首先是存放在帧存之中,然后才送出去显示的,因此帧存的设计是图形显示系统设计的一个关键。传统上,可以用来设计帧存的存储器件有多种,如DRAM、VR

- 关键字:

FPGA 帧

- FPGA构成3/3相双绕组感应发电机励磁控制系统 1系统简介3/3相双绕组感应发电机带有两个绕组:励磁补偿绕组和功率绕组,如图1所示。励磁补偿绕组上接一个电力电子变换装置,用来提供感应发电机需要的无功功率,使功率绕

- 关键字:

FPGA 双绕组 感应发电机 励磁控制

- 在可靠的通信系统中,要保证接收端能正确解调出信息,必须要有一个同步系统,以实现发送端和接收端的同步,因此同步提取在通信系统中是至关重要的。一个简单的接收系统框图如图1所示。 本文介绍一种基于现场可编程门

- 关键字:

FPGA 帧同步 法的研究

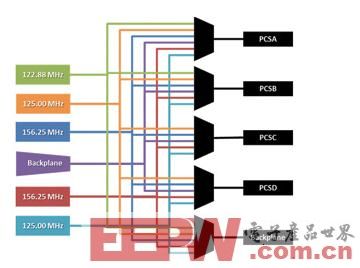

- 同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移和抖动)方面,还有那些组成时钟分配网络的组件。

FPGA开发团队不断面临过于繁琐、复杂的时钟网络的挑战。各种因素,包括不断增加的I/O需求、降低成本的要求和减少印刷电路板设计更改的需要,迫使设计人员重新审视时钟网络。本文将探讨FPGA时钟分配控制方面的挑战

- 关键字:

FPGA 时钟

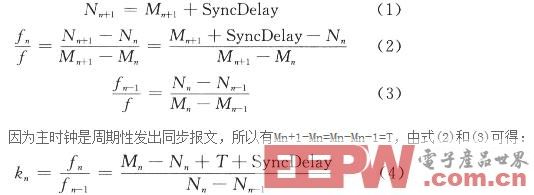

- 网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速度为1 500~1 800m/min,同步运行的电机之间1μs的时间同步误差将造成30 μm的运动误差。高速加工中心中加工速度为120 m/min时,伺服电机之间1μs的时间同步误差,将造成2 μm的加工误差,影响了加工精度的提高。

分布式网络中节点的时钟通常是采用晶振+计数器的方式来实现,由于晶振本身的精度以及稳定性问题,造成了时间运行的误差。时

- 关键字:

FPGA 时钟频率

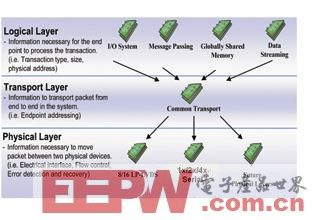

- 随着诸如无线、有线和医疗/图像处理应用的带宽需求不断提高,设计师们必须依赖必要的工具集来获得其所需的实时信号处理功能。在无线领域,例如现有的3G 网络覆盖,如HSPA+和EV-DO(即3G+)以及现在新兴的4G部署,主要的关注焦点在于数据吞吐量和回传的要求。它们要能够支持迅速增长的用户群,以及使用这些技术实现的无数视频和数据应用。因此就需要高速处理能力,以及同样重要的高度可靠、高吞吐量和低延迟的接口协议,来支持这些应用中所必需的各种DSP(DSP farm)、协同处理和桥接应用的需要。并且与大多数系统

- 关键字:

FPGA RapidIO

- 摘要:随着FPGA容量、功能以及可靠性的不断提高,采用FPGA设计数字电路已经成为数字电路系统领域的主要设计方式。在以DSP为主处理器,FPGA为协处理器,基于“软件无线电”技术的TD-SCDMA通用开发平台中,成功地采用FPGA完成一系列数据量大、重复性强、速度要求高的数字信号处理运算和相关数据接口。在这种平台中采用不同的软件,便可以对TD-SCDMA协议栈软件、物理层软件、手机芯片和移动终端等相关产品进行测试验证,具有很好的市场前景。

随着微电子技术的飞速

- 关键字:

FPGA TD-SCDMA

fpga+mpu+mcu介绍

您好,目前还没有人创建词条fpga+mpu+mcu!

欢迎您创建该词条,阐述对fpga+mpu+mcu的理解,并与今后在此搜索fpga+mpu+mcu的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473