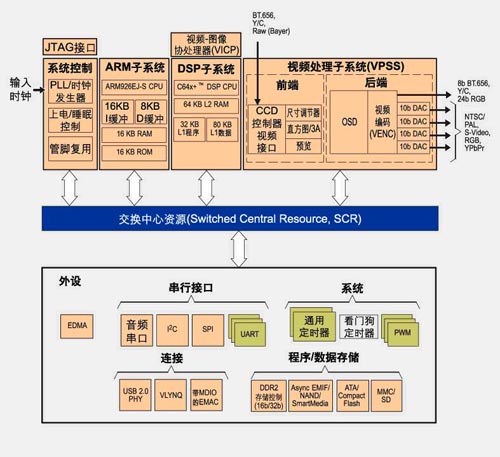

数字视频技术无疑将重塑整个电子行业的面貌。当然,数字视频技术也正在使我们的视频体验、传输以及交互方式发生着深刻的变化,开始进入汽车、计算机、移动电话及网络。过去,工程师们在实施数字视频时选择非常有限,硬连线以及基于ASIC的方案总是限制着器件的用途、功能,以及它们的自适应性;虽然专用器件的灵活性稍高于ASIC,但是,面对日新月异的多媒体标准与应用,它们的效用仍然很有限;而且缺少具有足够性能、成本足够低、灵活性足够高的数字视频开发平台。

为了解决这些难题,德州仪器公司提供了一种很好的解决方案,即基

关键字:

达芬奇 DSP ARM9

德州仪器 (TI) 公司的开放式多媒体应用平台OMAP(Open Multimedia Application Platform)是一种为满足移动多媒体信息处理及无线通信应用开发出来的高性能、高集成度嵌入式处理器。本文介绍基于OMAP经典设计汇总,供大家参考。

OMAP5912双核通信及其数字音频系统实现

OMAP平台因其特有的双核结构,广泛应用于实时多媒体影音数据处理、语音识别系统、网络通信等领域。笔者以OMAP5912平台的数字音频系统为例介绍双核通信的具体应用,希望能对使用OMAP的

关键字:

OMAP 示波器 DSP

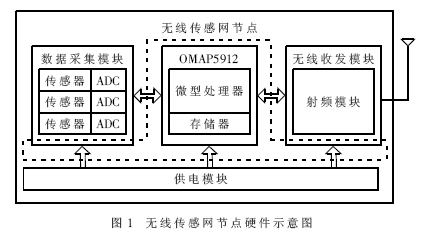

无线传感网络是计算技术、通信技术和传感器技术相结合的产物。传感网应用场合非常广泛,节点也可以搭载不同类型的传感器。当节点自身搭载的传感器为震动、磁传感器时,采集到的数据量较小,处理简单,目前的传感网节点(如Mica节点)就可以满足需要。但当节点集成图像传感器、红外传感器等大数据量传感器对传感数据网络的实时要求相当高时,现有的节点受处理及存储能力的限制无法满足要求。

本文主要分析在设计较高处理及存储能力传感节点时,如何满足传感网节点低功耗和高处理能力间的平衡关系,并介绍基于OMAP处理器的节点处理

关键字:

OMAP DSP

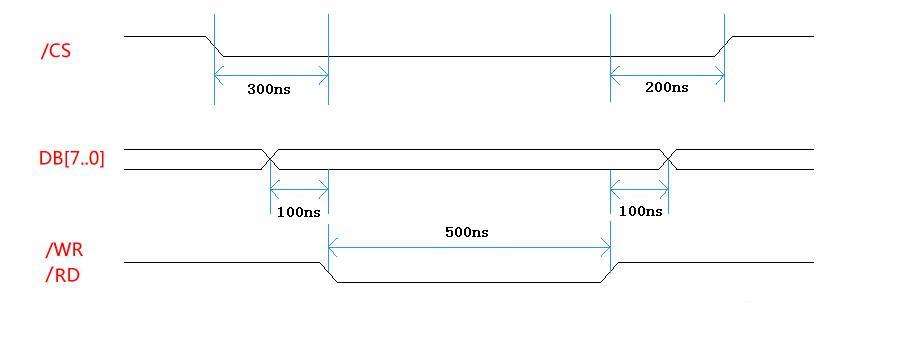

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下:

0.核心频率约束

这是最基本的,所以标号为0.

1.核心频率约束+时序例外约束

时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay.但这还不是最完整的时序约束

关键字:

FPGA 时序约束

FPGA采用了逻辑单元阵列概念,内部包括可配置逻辑模块、输出输入模块和内部连线三个部分。每一块FPGA芯片都是由有限多个带有可编程连接的预定义源组成来实现一种可重构数字电路。

长久以来新型FPGA的功能和性能已经为它们赢得系统中的核心位置,成为许多产品的主要数据处理引擎。

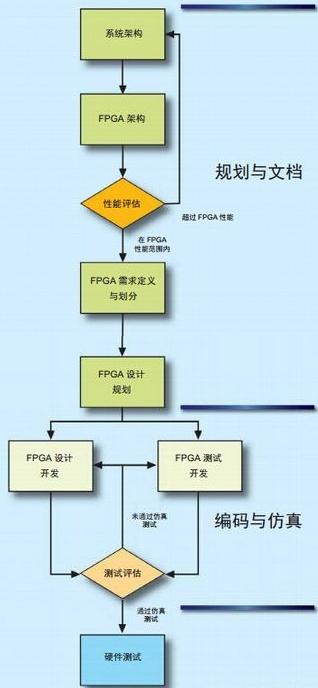

鉴于FPGA在如此多应用中的重要地位,采取正式且注重方法的开发流程来处理FPGA设计比以往更加重要。该流程旨在避免开发周期后期因发现设计缺陷而不得不进行费时费钱的设计修改,而且该缺陷还可能对项目进度计划、成本和质量造成灾

关键字:

FPGA

按照基于Windows的语言(C、C++、C#)等编程语言的初学入门教程,第一个历程应该是“Hello World!”的例程。但由于硬件上的驱动难易程度,此例程将在在后续章程中推出。硬件工程师学习开发板的第一个例程:流水灯,一切美好的开始。

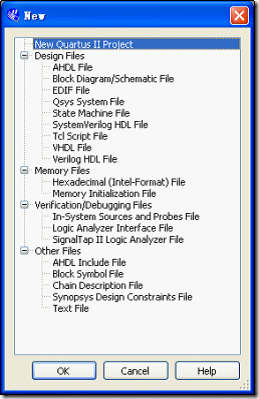

本章将会在设计代码的同时,讲解Quartus II 软件的使用,后续章节中只讲软件的思想,以及解决方案,不再做过多的累赘描述。

一、Step By Step 建立第一个工程

(1)建立第一个工程,File-New-New

关键字:

FPGA Quartus II

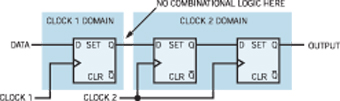

说到异步时钟域的信号处理,想必是一个FPGA设计中很关键的技术,也是令很多工程师对FPGA望而却步的原因。但是异步信号的处理真的有那么神秘吗?那么就让特权同学和你一起慢慢解开这些所谓的难点问题,不过请注意,今后的这些关于异步信号处理的文章里将会重点从工程实践的角度出发,以一些特权同学遇到过的典型案例的设计为依托,从代码的角度来剖析一些特权同学认为经典的跨时钟域信号处理的方式。这些文章都是即兴而写,可能不会做太多的分类或者归纳,也有一些特例,希望网友自己把握。

另外,关于异步时钟域的话题,推荐大家

关键字:

FPGA MCU

只有最初级的逻辑电路才使用单一的时钟。大多数与数据传输相关的应用都有与生俱来的挑战,即跨越多个时钟域的数据移动,例如磁盘控制器、CDROM/DVD 控制器、调制解调器、网卡以及网络处理器等。当信号从一个时钟域传送到另一个时钟域时,出现在新时钟域的信号是异步信号。

在现代 IC、ASIC 以及 FPGA 设计中,许多软件程序可以帮助工程师建立几百万门的电路,但这些程序都无法解决信号同步问题。设计者需要了解可靠的设计技巧,以减少电路在跨时钟域通信时的故障风险。

基础

从事多时钟设计的第一

关键字:

FPGA 异步信号 FIFO

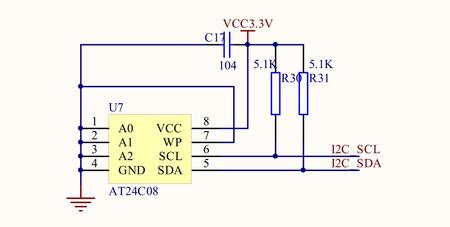

相信学过单片机的同学对I2C总线都不陌生吧,今天我们来学习怎么用verilog语言来实现它,并在FPGA学习版上显示。

i2c总线在近年来微电子通信控制领域广泛采用的一种新型的总线标准,他是同步通信的一种特殊方式,具有接口少,控制简单,器件封装形式小,通信速率高等优点。在主从通信中,可以有多个i2c总线器件同时接到i2c总线上,所有与i2c兼容的器件都有标准的接口,通过地址来识别通信对象,使他们可以经由i2c总线互相直接通信。

i2c总线由两条线控制,一条时钟线SCL,一条数据线SDA,这

关键字:

FPGA i2c verilog

市场研究机构ICInsights最新报告称,中国IC设计企业在2014年全球前五十无晶圆厂IC供应商排行榜上占据9个席位。这9家厂商包括海思、展讯、大唐微、南瑞智芯、华大、中兴、瑞芯微、锐迪科、全志。而2009年只有1家企业入围,这表明中国无晶圆厂IC产业确实成长显著。

然而,上述9家入围企业中,有5家都聚焦于目前最热门的智能手机市场。当然,这些年智能手机终端产业确实增长迅速,也为中国IC设计提供了发展空间和机遇。但我国拥有的是全球最大的信息消费市场,每年进口集成电路产品超过2000亿美元,对I

关键字:

海思 展讯 FPGA

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下:

0.核心频率约束

这是最基本的,所以标号为0.

1.核心频率约束+时序例外约束

时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay.但这还不是最完整的时序约束

关键字:

FPGA 时序约束

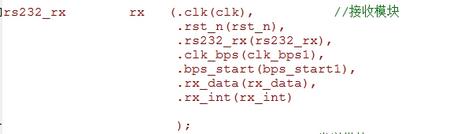

以前在学单片机的时候,觉得串口通信其实很简单,只要一个指令数据就能轻易的接收或者发送。前几天试着用FPGA实现,发现里面的学问还不少,并没有想象的那么简单。当然代码肯定是参考别人的,不过我还是认真研究了整段代码的,下面的程序就是我在看懂了别人代码后自己敲的,花了也不少时间,理解的也差不多,下面我就在这里给那些和我一样的初学者介绍一下吧,解释的不对的地方还望各位大神指正,大家好一起学习~

1、顶层模块

写程序都一样,不能多有的程序都写在一个模块里,那样看起来很麻烦,出了错误也不好维护,对于一

关键字:

FPGA 状态机

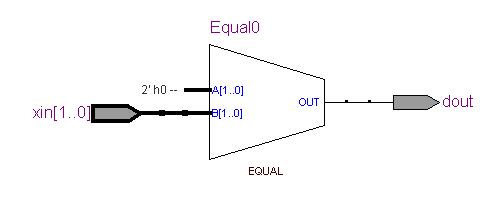

一、关于HDL

1. HDL简介

HDL : Hardware Discription Language 硬件描述语言,即描述FPGA/CPLD内部逻辑门的工作状态,来实现一定电路。

随着EDA技术的发展,使用硬件语言设计PLD/FPGA成为一种趋势。目前硬件描述语言有VHDL、Verilog、Superlog、System C、Cynlib C++、C Level等。 各种语言有各种优势,根据业界应用而定。

2. VHDL和Verilog区别

在业界,VHDL和Veri

关键字:

FPGA Verilog

刚开始玩CPLD/FPGA开发板的时候使用的一块基于EPM240T100的板子,alter的这块芯片虽说功耗小体积小,但是资源还是很小的,你写点稍微复杂的程序,如果不注意coding style,很容易就溢出了。当时做一个三位数的解码基本就让我苦死了,对coding style的重要性也算是有一个比较深刻的认识了。

后来因为一直在玩xilinx的spartan3 xc3s400,这块芯片资源相当丰富,甚至于我在它里面缓存了一帧640*480*3/8BYTE的数据都没有问题(VGA显示用)。而最近

关键字:

FPGA verilog RTL

学习FPGA其实也不算久,开始的时候参考别人的代码并不多,大多是自己写的,那时候做时序逻辑多一些。参加了中嵌的培训班,一个多月的时间在熟悉ISE软件的使用以及verilog语法方面下了苦功,也参考了不少书,算是为自己打下了比较好的基础。因为那时候培训的方向是软件无线电方面的,所以做了很多有关的模块程序,之前的日志里也发表了很多,关键是一个兴趣,感觉仿真后看到自己的一个个算法思想得到实现真有成就感。后来停了一段时间,因为实在没有比较有意思的活干了。

直到前段时间开始使用SP306的开发板,然后会参

关键字:

FPGA verilog

fpga+dsp介绍

您好,目前还没有人创建词条fpga+dsp!

欢迎您创建该词条,阐述对fpga+dsp的理解,并与今后在此搜索fpga+dsp的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473