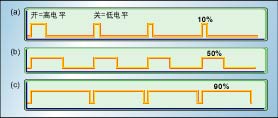

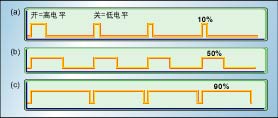

- 脉宽调制(PWM)是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术,广泛应用在从测量、通信到功率控制与变换的许多领域中。

理论基础

Ø冲量相等而形状不同的窄脉冲加在具有惯性的环节上时,其效果基本相同

Ø冲量指窄脉冲的面积

Ø效果基本相同,是指环节的输出响应波形基本相同

Ø波形基本相同含义:低频段非常接近,仅在高频段略有差异

模拟电路

模拟信号的值可以连续变化,其时间和幅度的分辨率都没有限制

- 关键字:

PWM DSP

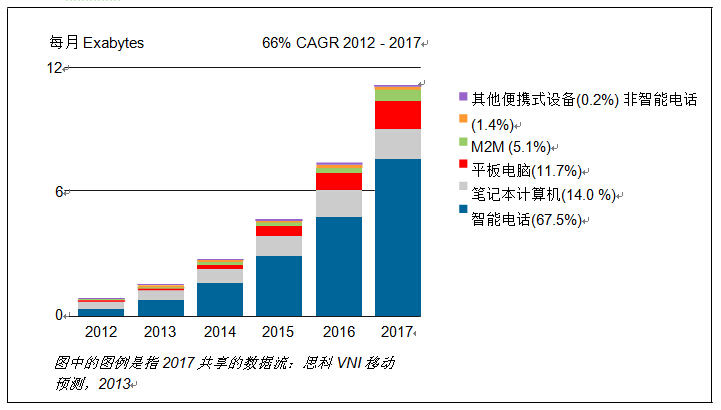

- 现在,总是忙个不停的消费者们希望能够随时随地保持连接,获取信息。可穿戴设备能够很方便地帮助消费者将上面的愿望变成现实。只需轻轻一点和一滑,或者使用手势,亦或是说出简单的语音指令,消费者就能立即访问所需的内容。随着可穿戴设备变得越来越智能,功能越来越丰富,OEM厂商们需要的解决方案不仅要能够提供下一代可穿戴设备所需的功能,还要满足这些小型设备对于尺寸和功耗的要求。

为了满足可穿戴设备市场的需求,莱迪思特别推出了适用于移动应用的FPGA器件,能够满足尺寸和功耗方面的需求,并可进行客制化以实现与接口/

- 关键字:

莱迪思 FPGA

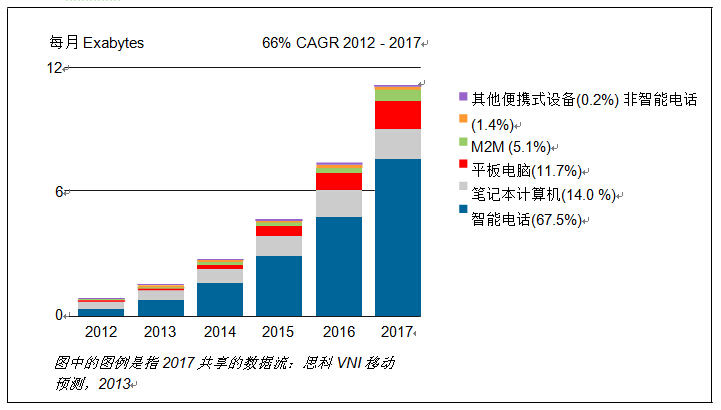

- 无线通信网络在短短30年间,已经将44亿人连接在一起。无线网络极大提升了我们在教育、商务、联络和生活等方面的质量,令我们获益匪浅。5G是下一代的无线网络,将会为我们带来更丰富的功能和受益。它可将数据速率提升100倍,所连接的设备也将增加100倍。要真正实现5G网络,我们必须解决很多技术上和商业上的挑战。我认为,仅仅靠半导体产业和系统产业解决不了这些挑战。 因此,我们必须充分挖掘同学们的天赋和潜力。这就是我们联合西安电子科技大学、友晶举办首次5G大赛的原因,我相信很多同学有很大的潜力,能够为未来5G网络

- 关键字:

Altera FPGA

- 许多好莱坞电影中用语音控制汽车或者其他机器人的场景想必大家并不陌生,如何能实现这样充满未来感的技术应用是目前许多厂商都在纷纷尝试的方向。现在已经也有一些利用语音进行控制的设备或者软件,例如苹果系统的语音识别功能,导航软件的自动搜索功能等等。 陆磊 ADI公司DSP亚洲业务区域经理 有人说语音识别是继触控技术之后的下一代“人机界面”,对此ADI公司DSP亚洲业务区域经理陆磊认为:目前为止,语音识别还不能完全替代传统的“人机界面”。但是有较大的潜力,对一些相对简单的控制,比如控制家电的开关等

- 关键字:

ADI DSP

- 纵观历史,电路内仿真 (ICE) 模式是使用硬件仿真器的第一种方式,也是迄今为止最为流行的方法。在这种模式中,需将硬件仿真器插入物理目标系统上的插孔,以此代替待开发的芯片,从而利用实时数据支持运用和调试硬件仿真器内部映射的待测设计(DUT)。 然而,这种公认的能够引人注目的验证方法却存在一系列问题,其中最严重的问题便是它的随机性。也就是说,当调试DUT时,它缺少确定性或者可重复性。为了更好地理解这一点,我们可以做个形象类比。 让我们来看看双向飞碟射击。这是一种射击运动,在这项运动中,会将碟靶从靶场

- 关键字:

SoC FPGA

- All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. )今天宣布支持16nmUltraScale+™系列的工具及文档面向公众公开提供,其中包含Vivado® 设计套件HLx版、嵌入式软件开发工具、赛灵思Power Estimator (功耗评估器),以及用于Zynq® UltraScale+ MPSoC及Kintex® UltraScale+器件的技术文档。设计开发者们现在就可以在自己特定的设计上,通过UltraScale+产品系列实现比28nm器件高出2-5

- 关键字:

Xilinx FPGA

- 国产FPGA啊,以前想都不敢想,但是越有难度越有人去啃。

- 关键字:

京微雅格 FPGA

- 山东高云半导体科技有限公司(以下简称“高云半导体”今日宣布,在山东省国产IP软核平台上发布三个IP软核参考设计,分别是:I2C总线、SPI、UART,作为星核计划取得的初步成果,这三个软核在工业控制、系统调试以及嵌入式开发中具有非常广泛的应用。 “山东省国产IP软核平台由山东信息通信研究院、高云半导体共同发起,致力于打造国内首家国产IP软核资源库”,山东高云半导体科技有限公司总经理梁岳峰先生表示,“该平台以山东信息通信研究院的集成电路设计测试平台、高云半导体星核计划为依托,本着开放、资源共享的原则,

- 关键字:

高云 半导体 FPGA

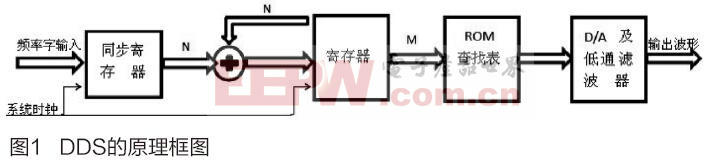

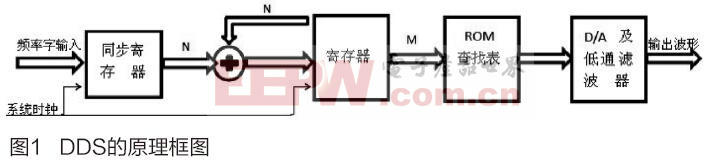

- 最近接了一个项目吧,是我们学校物理院院长带的研究生搞的,小墨有幸跟他们合作,负责FPGA方面的工作,完成后据说还会申请国家专利,具体到什么时候完成,那可能就是猴年马月了,或者说我已经不在学校了。从今天开始,小墨将开始接触赛灵思公司的FPGA(老师提供的平台),用到的当然是SOPC。其实做做项目也好,让自己锻炼一下,我也好久没有做大一点的项目了,对我来说也是一个机会吧。 信号发生器这个东西相信大家都知道,关于基于DDS信号发生器的技术文档网上也多的是,但是我还是想写一下这部分的教学,因为从我自身的学习

- 关键字:

FPGA SOPC

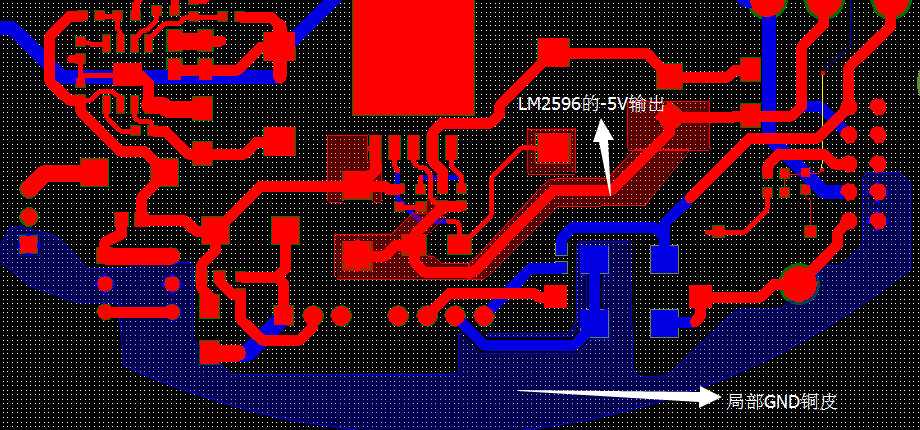

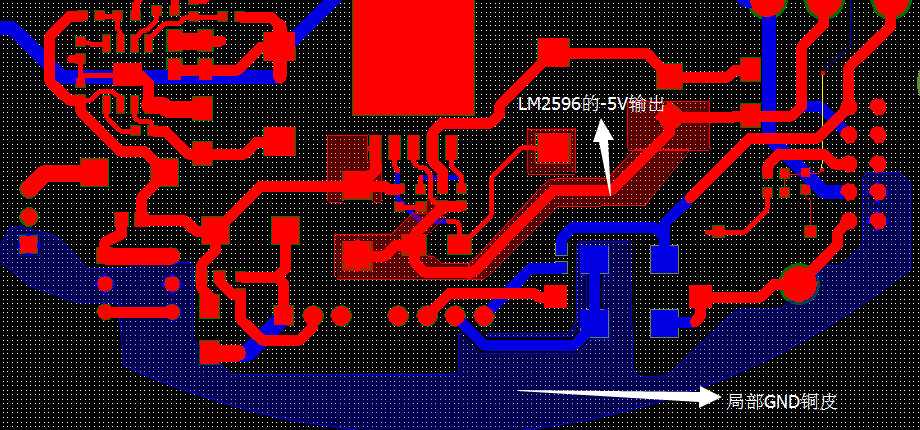

- 想要成为一名硬件工程师首先必须掌握的就是PCB的设计与绘制,这里我们为大家整理了几条设计技巧。 1、如果设计的电路系统中包含FPGA器件,则在绘制原理图前必需使用Quartus II软件对管脚分配进行验证。(FPGA中某些特殊的管脚是不能用作普通IO的)。 2、4层板从上到下依次为:信号平面层、地、电源、信号平面层;6层板从上到下依次为:信号平面层、地、信号内电层、信号内电层、电源、信号平面层。6层以上板(优点是:防干扰辐射),优先选择内电层走线,走不开选择平面层,禁止从地或电源层走线(原因:会分

- 关键字:

PCB FPGA

- 摘要:在科技飞速发展的今天,各种自动化仪器及自动控制都离不开信号采集,而且要采集的信号越来越快,精度要求也越来越高。如何简单快速的让系统集成这项功能呢?

1、ZSDA1000的基本介绍 ZDS1000是ZLG致远电子开发的高速信号数据采集模块,模块通过PCI Express2.0接口与主机端连接,350M带宽,1GSa/s的采样速率。用户只需要通过动态链接库文件就可以轻松控制模块进行数据采集和数据处理。可用于质谱分析、雷达信号捕捉、材料分析等场

- 关键字:

FPGA ZSDA1000

- 本文利用直接数字合成技术通过一款FPGA可编程逻辑芯片实现函数信号发生器的研制,该信号发生器是以Altera公司生产的EP4CE6F17C8芯片为设计载体,通过DDS技术实现两路同步信号输出。通过软件Quartus-II12.0和Nios-II 12.0开发环境编程,实现多种波形信号输出,信号具有高精度的频率分辨率能力,最高可达36位。最后通过实验输出的波形信号符合标准。

- 关键字:

直接数字合成技术 FPGA 信号发生器 Quartus-II 201512

- 本白皮书介绍为什么电信带宽和基础设施促进了FPGA功能的增强,以及ASIC和ASSP面临的商业挑战,可编程逻辑器件(PLD)定制方法是怎样支持FPGA功能的跨越式发展。本文还简要介绍了下一代FPGA和SoC系列品。 引言 最新发布的FPGA是硬件规划人员、软件开发人员和系统设计人员实现其下一代产品目标的关键支撑因素。大量的电信基础设施成指数增长的带宽需求以及各行业使用这些带宽的需求使得现有硬件和软件解决方案很难满足性能要求,也难以达到成本和功耗目标。ASIC、ASSP和独立处理器遇到了发展瓶颈,P

- 关键字:

FPGA SoC

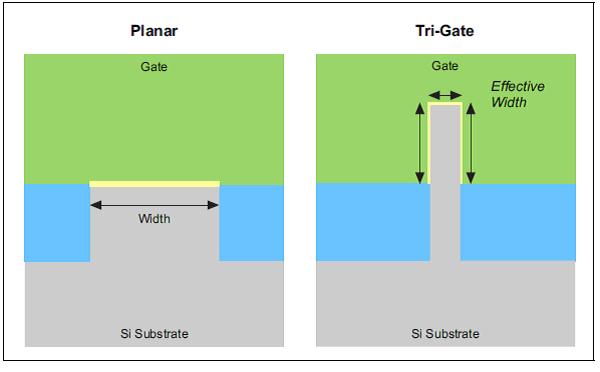

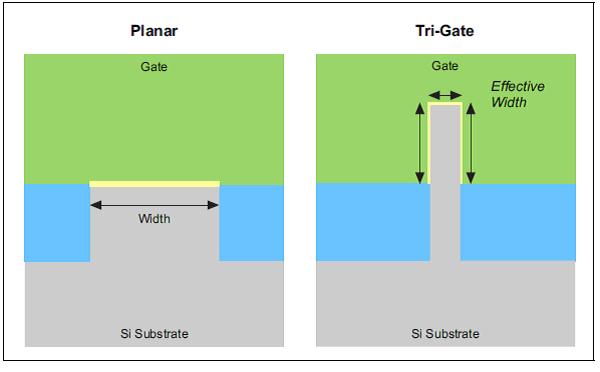

- 引言 2013年2月,Altera公司与Intel公司共同宣布了Altera下一代最高性能FPGA产品的生产将独家采用Intel的14nm 3D Tri-Gate(三栅极)晶体管技术。这使得Altera成为当前采用最先进、最高性能半导体技术的独家专业FPGA供应商。本文介绍了三栅极及相关技术的历史与现状,以便了解三栅极技术对高性能FPGA性能的影响,以及其在数字电路速度、功率以及生产方面有何种程度的优势。 晶体管设计的背景 1947年,贝尔实验室展示了第一支晶体管,采用的是锗

- 关键字:

Altera FPGA

- Altera公司今天宣布,开始提供面向Nios® II嵌入式处理器的Altera®功能安全锁步解决方案,这一解决方案降低了设计周期风险,帮助系统设计人员简化工业和汽车安全应用的认证。Altera与意大利比萨的功能安全领先供应商YOGITECH联合开发的锁步解决方案采用了Altera FPGA、SoC,认证工具流程,以及YOGITECH的知识产权(IP)内核。这一解决方案帮助客户在Altera FPGA中轻松实现SIL3安全设计,包括低成本Cyclone® V&n

- 关键字:

Altera FPGA

fpga+dsp介绍

您好,目前还没有人创建词条fpga+dsp!

欢迎您创建该词条,阐述对fpga+dsp的理解,并与今后在此搜索fpga+dsp的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473