- 智能型片上通信解决方案领先供应商美商芯网股份有限公司(Sonics, Inc.)今天宣布,中国发展最快的创新型系统及硅提供商之一——北京新岸线公司(Nufront)已选择Sonics的片上网络IP解决方案和性能分析工具,来开发其全新的先进笔记本和平板电脑产品系列。新岸线公司面向移动计算机的高集成、低功耗SoC解决方案系列位列市场同类产品前茅,在性能和性价比方面属于行业最佳。新岸线将获得授权使用Sonics著名的SonicsMX低功耗片上网络以及高效的MemMax内存调度器。

- 关键字:

Sonics SoC

- ARM和中芯国际集成电路制造有限公司(中芯国际)日前宣布双方将在中芯65纳米和40纳米低漏电工艺节点上合作开发先进的ARM物理IP库平台。该协议将免费提供ARM的DesignStart 在线IP访问入口供双方客户使用,可下载9轨和12轨multi-Vt 逻辑库套件,电源管理包,ECO 包和ARM优化的高密度存储编译器。该协议扩展了双方长期合作关系,以提供双方客户得以用于180纳米,130纳米,110纳米和90纳米的工艺技术上具高度差异化的IP。

- 关键字:

ARM SoC

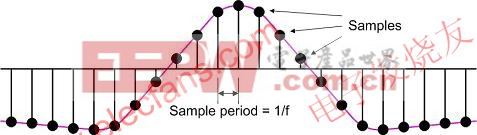

- 基于中档FPGA多相滤波器的设计实现, 在现代电子系统中,到处都可以看到数字信号处理( DSP )的应用,从MP3播放器、数码相机到手机。DSP设计人员的工具箱的支柱之一是有限脉冲响应( FIR )滤波器。FIR滤波器越长(有大量的抽头),滤波器的响应越好。然而这

- 关键字:

设计 实现 滤波器 多相 FPGA 基于

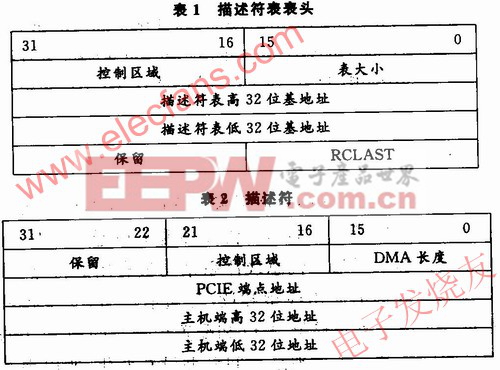

- 基于FPGA的PCIE总线扩展卡的设计, PCIE(PCI express)是用来互联诸如计算机和通信平台应用中外围设备的第三代高性能I/0总线。PCIE体系结构继承了第二代总线体系结构最有用的特点,采用与PCI相同的使用模型和读/写通信模型,支持各种常见的事务。其存

- 关键字:

扩展 设计 总线 PCIE FPGA 基于

- 可程序逻辑闸阵列芯片(FPGA)双雄赛灵思(Xilinx)与阿尔特拉 (Altera)先后推出28纳米FPGA产品,不仅使FPGA市场战火升温,也让晶圆代工市场激烈角逐,在Xilinx首度与台积电携手合作后,Altera在28纳米产品的布局上亦相当积极,近期亦展示在28纳米 FPGA平台上的25-Gbps收发器,FPGA双雄的激烈竞赛,预料台积电将成为最大受惠者。

Altera指出,在28纳米FPGA中展示25-Gbps收发器,是收发器产品的里程碑,该芯片是Altera用于在28纳米FPGA上,

- 关键字:

Xilinx FPGA 28纳米

- 嵌入式系统是泛计算领域的重要组成部分,是嵌入式对象宿主体系中完成某种特定功能的专用计算机系统。嵌入...

- 关键字:

微处理器技术 嵌入式系统 SOC

- 无论为数以百万计的用户搜索请求提供服务还是处理超大量的信息,都需要数量庞大的计算资源,进而消耗大量能源。事实上,用于计算与冷却的能耗费用是数据中心运营的最大成本 [1]。随着数据中心的数量和规模不断增长,

- 关键字:

FPGA 绿色搜索技术

- 摘 要: 提出了一种将堆栈空间划分为任务栈和中断嵌套栈的设计结构,使堆栈空间最小化。采用VHDL硬件语言,在FPGA设备上模拟实现了具有自动检验功能的栈空间管理器。栈空间管理器由不同功能的逻辑模块组成,主要阐

- 关键字:

FPGA 栈空间 管理器

- 摘 要: 为满足三维大地电磁勘探技术对多个采集站的同步需求,基于FPGA设计了一种晶振频率校准系统。系统可以调节各采集站的恒温压控晶体振荡器同步于GPS,从而使晶振能够输出高准确度和稳定度的同步信号。系统中

- 关键字:

FPGA 恒温晶振 频率校准 系统

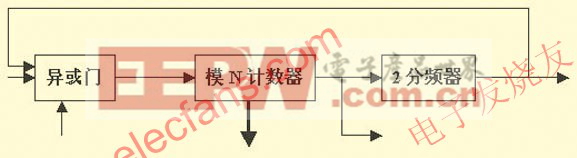

- 基于VHDL和FPGA的多种分频的实现方法,分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。在同一个设计中有时要求多种形式的分频。通常由计数器或计数器的级联

- 关键字:

实现 方法 多种 FPGA VHDL 基于

- 摘 要:为了有效防止机械式键盘按键抖动带来的数据错误,这里在Quartus Ⅱ开发环境下,采用VHDL 语言设计了一种能够将机械式4 times;4 矩阵键盘的按键值依次显示到8 个7 段数码管上的矩阵键盘及显示电路。仿真结果表

- 关键字:

FPGA/ CPLD 键盘 电路

- 全球可编程逻辑解决方案领导厂商赛灵思公司,2010年9月14日宣布与四川虹视显示技术有限公司(简称四川虹视)在成都高新区共同成立FPGA联合实验室, 致力于推动虹视公司最新的OLED产品技术研发,赛灵思全球消费市场总监Harry Raftopoulos,高级技术市场经理酆毅,四川虹视总经理郎丰伟,技术总监文东星、产品研发中心部长田朝勇等出席了签字揭牌仪式。

根据双方当天签署的协议,赛灵思公司计划向四川虹视提供技术培训,以及多套开发工具,如Spartan®-6 消费视频开发套件,Spart

- 关键字:

赛灵思 FPGA

- TSMC 5日宣布,硅知识产权联盟的结盟范围将扩大至Soft IP业者,未来将有完备的Soft IP供先进技术使用,进而加速客户产品的上市时程。

经由此一Soft IP结盟方案,TSMC将提供特定的设计文件与技术资讯,让技术伙伴得以充分地将Soft IP在TSMC的技术基础上予以最佳化。同时,TSMC也与这些公司合作,使其soft IP的发展与公司的工艺技术发展时程达到一致,以加速他们soft IP准备就绪的时程。

一直以来,Soft IP的发展独立于工艺技术之外已行之有年,也因此Soft

- 关键字:

IP SoC

- FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的...

- 关键字:

FPGA 全局时钟 BUFG

- 提出了一种基于FPGA的双通道旋转变压器测角电路设计方案,通过FPGA来控制AD2S82A、AD2S80A的解码和同步问题。同时用FPGA对转换后数据进行误差补偿和组合,以及二进制角度值的转换,提高了整个系统的集成度和可靠度。整个电路在Altium Designer 9.O设计环境下设计实现。采用Altera公司的EP2C35F484C6型FPGA芯片进行FPGA部分的仿真,实验和仿真的结果很好地实现了该方案的设计功能,并满足高精度、高速度转换的设计要求。

- 关键字:

FPGA 双通道 测角系统 旋转变压器

fpga soc介绍

您好,目前还没有人创建词条fpga soc!

欢迎您创建该词条,阐述对fpga soc的理解,并与今后在此搜索fpga soc的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473