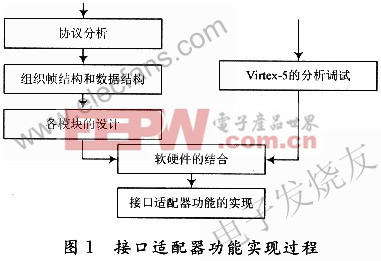

- 采用上位机与FPGA开发板的光纤通道接口适配器设计,随着存储技术的迅速发展,存储容量得到了迅速的增长,存储系统的数据传输速度成为了主要的瓶颈。光纤的传输具有其速度上的优势,然而,在光纤传输要受到光纤通道接口的限制,因此光纤通道应用于高速数据传输的一个关

- 关键字:

接口 适配器 设计 通道 光纤 上位 FPGA 开发 采用

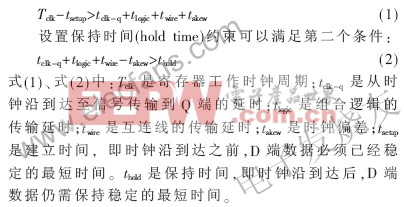

- SOC时序分析中的跳变点介绍, 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这在SOC设计后期,也就是要对时序签字时可能会导致问

- 关键字:

介绍 分析 时序 SOC

- 系统芯片ZSU32在SoC芯片设计中的应用,本文针对中山大学ASIC设计中心自主开发的一款系统芯片ZSU32,以Synopsys公司的Design Compiler为综合工具,探索了对SoC芯片进行综合的设计流程和方法,特别对综合过程的时序约束进行了详细讨论,提出了有效的综合约束

- 关键字:

芯片 应用 设计 ZSU32 系统 SoC

- 利用Java良好的移植特性的FPGA可编程嵌入式系统,传统的嵌入式产品只能实现某种特定的功能,不能满足用户可变的丰富多彩的应用需求。为解决这个问题,本文设计并实现了一种使用Java作为软件平台的基于FPGA的可编程嵌入式系统,以实现系统对多种本地应用和网络的支持

- 关键字:

可编程 嵌入式 系统 FPGA 特性 Java 良好 移植 利用

- FPGA全局时钟资源相关Xilinx器件原语及使用,FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。为了适应复杂设

- 关键字:

Xilinx 器件 使用 相关 资源 全局 时钟 FPGA

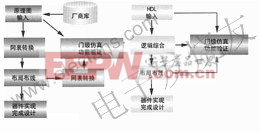

- FPGA/EPLD的自上而下设计方法及其优缺点介绍,FPGA/EPLD的自上而下(Top-Down)设计方法: 传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特

- 关键字:

缺点 介绍 及其 方法 自上而下 设计 FPGA/EPLD

- Altera公司(NASDAQ: ALTR)日前宣布,推出40-Gbps以太网(40GbE)和100-Gbps以太网(100GbE)知识产权(IP)内核产品。这些内核能够高效的构建需要大吞吐量标准以太网连接的系统,包括,芯片至光模块、芯片至芯片以及背板应用等。

- 关键字:

Altera FPGA

- 系统级芯片(SoC)解决方案被誉为半导体业最重要的发展之一,目前,从数字手机和数字电视等消费类电子产品到高端通信LAN/WAN设备中,这一器件随处可见。过去,为了创建此类嵌入式系统,设计工程师不得不在处理器、逻辑

- 关键字:

FPGA 方案 数字显示 系统设计

- 在汽车电子中广为采用的微控制器(MCU)正快速面临时间和成本的压力。使用MCU的主要优势一直以来都是lsquo;创造具有高性价比的高阶系统整合rsquo;。然而,在此一优势之下,有一些与元件本身相关的潜在成本是超乎于其

- 关键字:

FPGA 车用 微控制器

- 为了解决基于LabVIEWFPGA模块的DMAFIFO深度设定不当带来的数据不连续问题,结合LabVIEWFPGA的编程特点和DMA FIFO的工作原理,提出了一种设定FIFO深度的方法。对FIFO不同深度的实验表明,采用该方法设定的FIFO深度能够

- 关键字:

LabVIEW FPGA FIFO 模块

- 0 引言

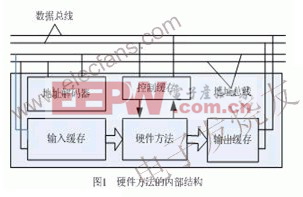

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-ok up table,LUT)结构,这种结构特别适用于并行处理结构,相对于传统方法来

- 关键字:

FPGA FIR 分布式算法 低通

- 温度测量主要有两种方式:一种是传统的接触式测量,另一种是以红外测温为代表的非接触式测量。传统的温度测量不仅反应速度慢,而且必须与被测物体接触。红外测温以红外传感器为核心进行非接触式测量,特别适用于高温

- 关键字:

SOC 高精度 红外测温 系统

- 摘要:为了产生稳定激励信号的目的,采用Verilog硬件语言在FPGA上实现了数字频率合成器的设计,该设计包括累加器、波形存储器、AD转换、低通滤波器等;对累加器、波形存储器都进行了仿真,并下载到FPGA中,经A/D转换

- 关键字:

FPGA 数字频率合成器

- 摘要:高量程加速度传感器在小信号的激励下输出在10 mV以内,传统测试系统的噪声可能覆盖如此小的电压信号,使高量程的加速度传感器无法测试小的加速度信号。针对这一问题提出了基于自动增益切换控制理论的自适应数字

- 关键字:

FPGA 数字 传感器设计

- 东芝在“2010 Symposium on VLSITechnology”上,发布了采用09年开始量产的40nm工艺SoC的低电压SRAM技术。该技术为主要用于便携产品及消费类产品的低功耗工艺技术。通过控制晶体管阈值电压的经时变化,可抑

- 关键字:

SRAM SoC 低电压

fpga soc介绍

您好,目前还没有人创建词条fpga soc!

欢迎您创建该词条,阐述对fpga soc的理解,并与今后在此搜索fpga soc的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473