莱迪思半导体公司 ,低功耗可编程器件的领先供应商,近日宣布推出全新Lattice Certus™-NX系列FPGA。该系列器件在通用FPGA市场上拥有领先的IO密度,每平方毫米的IO密度最高可达同类FPGA竞品的两倍。Certus-NX FPGA拥有卓越的低功耗、小尺寸、高可靠性和瞬时启动等特性,支持高速PCI Express(PCIe)和千兆以太网接口,可实现数据协同处理、信号桥接和系统控制。Certus-NX FPGA面向从自动化工业设备中的数据处理到通信基础设施中的系统管理等一

关键字:

FPGA 低功耗

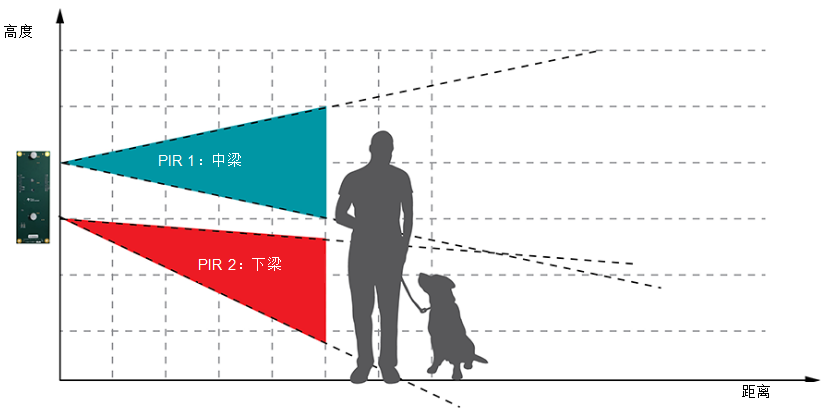

有用的物联网(IoT)程序被应用于几乎所有行业的纵向分支中,并有效扩展了旧有系统的实用性。例如,出于安全目的,住宅、商业和工业设施正在使用可视门铃。这些服务已经存在数十年,但通常仅限于可通过闭路电视网络提供昂贵的双向音频和单向视频功能的高端设备。但是,现在物联网技术无需大规模的同轴电缆或以太网基础结构即可实现此级别的安全性。本文将仔细研究与可视门铃相关的一些视频、音频和电源设计难题,以及解决这些难题所需的技术进步。无缝用户体验传统的可视门铃系统涉及使用按铃、麦克风和摄像机。这些系统通常被硬连接到电源,而视

关键字:

DSP CMOS PIR MCU IoT

Intel这几年全力投入AI人工智能,尤其在数据中心市场,拥有业内最完整的解决方案,Xeon CPU、Xe GPU(开发中)、Agilex FPGA、Movidius、Habana、eASIC……等等不一而足,可以灵活应对各种不同的工作负载,实现最优化加速。 今天,Stratix 10 FPGA家族迎来了最新成员“Stratix 10 NX”,号称第一款专为AI优化的FPGA,通过定制硬件集成了高性能AI,可带来高带宽、低延迟的A

关键字:

Intel AI Stratix FPGA

低功耗FPGA大厂莱迪思半导体(Lattice Semiconductor)近日推出全新FPGA软件解决方案Lattice Propel,提供扩充RISC-V IP及更多类型周边组件的IP函式库,并以「按建构逐步校正」(correct-by-construction)开发工具协助设计工作,进一步实现FPGA开发自动化。莱迪思最新推出的Lattice Propel开发工具包含两大特色:IP整合工具Lattice Propel Builder,以及软件开发工具Lattice Propel SDK。Lattic

关键字:

莱迪思 FPGA Propel RISC-V

英特尔公司近日正式发布第三代英特尔®至强®可扩展处理器及全新的AI软硬件产品组合,旨在进一步助力客户在数据中心、网络及智能边缘环境中加速开发和部署AI及数据分析工作负载。作为业界首个内置bfloat16支持的主流服务器处理器,第三代英特尔®至强®可扩展处理器能够帮助图像分类、推荐引擎、语音识别和语言建模等应用的AI推理和训练更简便地部署在通用CPU上。英特尔公司副总裁兼至强处理器与存储事业部总经理Lisa Spelman表示:“快速部署AI和数据分析对当今各类企业至关重要。英特尔一直致力于不断强化处理器的

关键字:

AI FPGA IoT IDC

新基建是数字技术的基础设施,具有发展速度快、技术含量高等特点,随着新技术新应用层出不穷,其对计算、架构、协议、接口的动态更新提出了新的需求,因此,对底层芯片提出了新的考验。FPGA具有软硬件可编程、接口灵活、高性能等优势,能够满足高新技术对于计算和连接的需求。那么,新基建将为FPGA带来哪些市场增量?又将提出怎样的技术挑战?我国FPGA企业该如何抓住新基建带来的发展机遇?新基建将大幅拉动FPGA新需求新基建是以技术创新和信息网络为基础,来推动基础设施体系的数字转型、智能升级以及融合创新等。在原型设计、协议

关键字:

FPGA 新基建 基础设施

全球领先的高性能传感器解决方案供应商、移动市场3D脸部识别领域领导者艾迈斯半导体(ams AG)近日宣布,推出两款新型位置传感器 — AS5147U和AS5247U,可降低系统成本,同时提高安全关键型汽车功能(如动力转向、主动减振器控制和制动)的电气化水平,有助于实现更安全、更智能、更环保的汽车。这两款新型位置传感器能够为汽车行业带来多种性能优势,并可降低系统成本。艾迈斯半导体AS5147U是一款智能旋转磁性位置传感器芯片,可用于转速高达28,000rpm的电机。新型AS5247U是一款双堆叠式裸片,可提

关键字:

SPI BLDC CRC DSP UVM

俄罗斯经受了西方一轮又一轮的制裁,却仍能在芯片短板之下推出一批又一批的尖端武器,那么,没有高端芯片对武器先进性影响究竟多大?俄采取了哪些措施弥补没有高端芯片带来的缺陷呢?

关键字:

芯片 DSP FPGA

专注于引入新品的全球电子元器件授权分销商贸泽电子 ( Mouser Electronics ) 近日与 Trenz Electronic 签署了全球分销协议。Trenz Electronic是工业级多处理器片上系统 (MPSoC) 模块化系统(SoM) 制造商,签约后,贸泽将分销Trenz Electronic公司基于Xilinx FPGA的一系列工业级MPSoC SoM。这些精选的SoM作为高性能解决方案,为所有板载电压提供强大的开关&nb

关键字:

MPSoC SoM FPGA

James Wilson (Silicon Labs时钟产品总经理) 1 从时钟角度看5G的特点 为了在全球范围内提供5G网络连接和覆盖,服务提供商们正在部署更多的无线设备,从大容量的宏基站到专注于扩展网络覆盖范围的小基站和毫米波解决方案。与4G网络将射频和基带处理放在一起不同,5G将这些资源分布在整个网络中,因此需要更大容量、更低延迟的前传和回传解决方案。如此广泛的应用需要大量的时钟发生器、时钟缓冲器、时钟去抖芯片、网络同步器和振荡器,来提供必要的时钟发生和分配功能。此外,5G网络有一个共同的需

关键字:

202006 Silicon Labs FPGA

自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.)近日宣布推出专为联网和存储加速而优化的 UltraScale+ FPGA 产品系列最新成员 Virtex® UltraScale+™ VU23P FPGA ,通过独特方式综合多种资源,实现了更高效率数据包处理和可扩展的数据带宽,致力于为联网和存储应用突破性的性能。在数据指数级增长对智能化、灵活应变的网络和数据中心解决方案提出极高要求的今天,全新 VU23P FPGA

关键字:

RAM FPGA

近日,为响应可编程逻辑技术的不断发展,Teledyne e2v进一步增强了其 数据转换器 产品组合以及支持它们运作的高速SERDES技术。为了辅助Xilinx热门产品20nm Kintex UltraScale KU060 FPGA,Teledyne-e2v现在可提供高度优化的多通道模数转换器(ADC)和数模转换器(DAC)解决方案。它们有各种不同等级类别可供选择,最高级别是高可靠性耐辐射的宇航级,适用于卫星通信、地球观测、导航和科学任务。每个新的数据转换器都可以通过其集成的

关键字:

ADC DAC FPGA

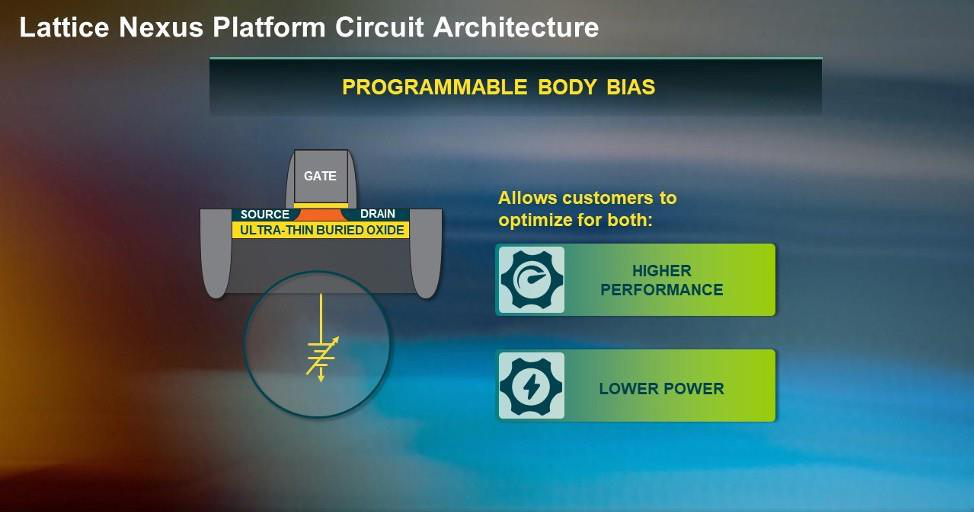

目录第一部分| 莱迪思Nexus重新定义低功耗FPGA第二部分| 莱迪思Nexus加速AI处理性能第三部分| 莱迪思Nexus FPGA提供高稳定性第四部分| 小尺寸不在话下第五部分| 莱迪思Nexus技术平台提供完善的系统解决方案第六部分|推出首款基于莱迪思Nexus的FPGA:CrossLink第七部分| 结论物联网AI、嵌入式视觉、硬件安全、5G通信、工业和汽车自动化等新兴应用正在重新定义开发人员设计网络边缘产品的硬件要求。为了支持这些应用

关键字:

PCB FPGA

国微思尔芯(“S2C”), 全球领先的前端电子设计自动化 (EDA) 供应商, 发布全球首款FPGA验证仿真云系统 Prodigy Cloud System。这是为下一代 SoC 设计验证需要而特别开发的验证仿真云系统,支持业界最大容量的 FPGA 元件 Xilinx Virtex? UltraScale? VU440 和 Intel? Stratix? 10 GX 10M, 可因需求扩充搭载的容量, 不受时间、地点的限制, 大幅缩短复杂 SoC的设计验证流程。

关键字:

国微思尔芯 FPGA Prodigy Cloud System

国微思尔芯(“S2C”), 全球领先的前端电子设计自动化 (EDA) 供应商, 发布全球首款FPGA验证仿真云系统 Prodigy Cloud System。这是为下一代 SoC 设计验证需要而特别开发的验证仿真云系统,支持业界最大容量的 FPGA 元件 Xilinx Virtex? UltraScale? VU440 和 Intel? Stratix? 10 GX 10M, 可因需求扩充搭载的容量, 不受时间、地点的限制, 大幅缩短复杂 SoC的设计验证流程。

关键字:

国微思尔 FPGA Prodigy Cloud System

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473