- 基于CPLD的DSP与声卡的接口技术,1引言使用复杂可编程逻辑器件(CPLD)可提高系统集成度、降低噪声、增强系统可靠性并降低成本,同时它不仅具有电擦除特性,而且出现了边缘扫描及在线编程等高级特性,因而可用于状态机、同步、译码、解码、计数、总线接

- 关键字:

接口 技术 声卡 DSP CPLD 基于

- 摘 要: 以Altera公司MAX7000系列为代表,介绍了CPLD在DSP系统中的应用实例。该方案具有一定的普遍适用性。

关键词: RESET BOOT HPI CPLD的延时 时序 DSP的速度较快,要求译码的速度也必须较快。利用

- 关键字:

CPLD DSP 系统 中的应用

- 1 引言

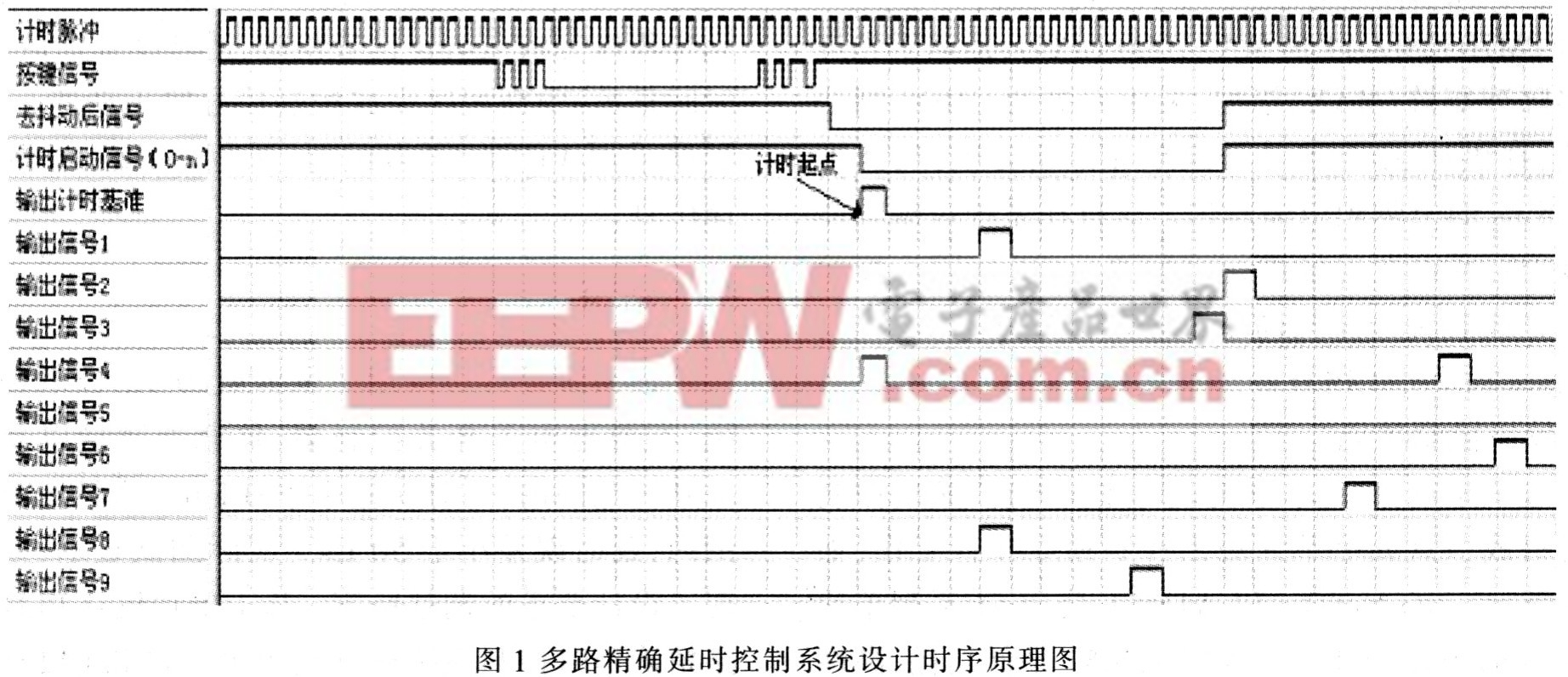

现代控制系统中控制对象可能是复杂、分散的,而且往往是并行、独立工作的,但整体上它们是相互关联的有机组合。因此,控制信号的时序逻辑则要求更加精确。CPLD单片机为控制系统提供了技术支持,由CPLD和

- 关键字:

控制系统 延时 精确 CPLD 单片机

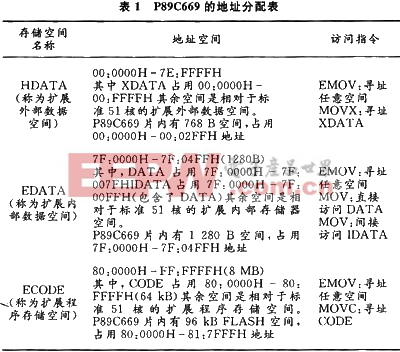

- 利用P89C669的23 b的线性地址并采用CPLD外部扩展,采用CPLD增强单片机P89C669外部设备扩展能力 2007.08.15 来自:现代电子技术 P89C669是PHILIPS半导体一款51MX(存储器扩展)内核的微处理器,其指令执行速度2倍于标准的80C51器件,线性地址经扩展后可支持高达8 MB的

- 关键字:

CPLD 外部 扩展 采用 地址 P89C669 线性 利用

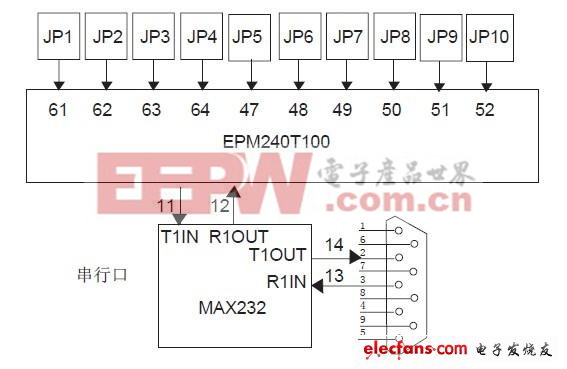

- 一、硬件电路设计 本文选用CPLD 是ALTERA 公司的EPM240T100,结合MAX232 接口芯片进行串口通信设计,框图如下图1 所示。 图1 CPLD串口通信模块硬件设计 二、VHDL程序模块设计及描述 使用VHDL 对CPL

- 关键字:

设计 通信 串口 CPLD

- 本系统是用CPLD实现的智能数字电压表。随着EDA技术的广泛应用,CPLD已成为现代数字系统设计的主要手段,CPLD目前正朝着更高速、更高集成度、更强功能和更灵活的方向发展。

- 关键字:

电压表 设计 数字 高精度 控制 核心 CPLD

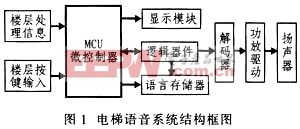

- 语音系统是电梯不可缺少的部分,用于楼层报数、方向提示、报警告示、消防对讲以及广告宣传等。传统语音系统绝大多数采用语音器存储和播放语音,但存在比如外电路复杂、音质差、成本高、容量小以及语音不易更改等缺陷。鉴于此,设计了一款基于CPLD和VS1011E解码器的电梯语音系统。

- 关键字:

语音系统 设计 电梯 解码器 CPLD VS1011E 基于

- 8位单片机在嵌入式系统中应用广泛,然而让它直接与PCI总线设备打交道却有其固有缺陷。8位单片机只有16位地址线,8位数据端口,而PCI总线2.0规范中,除了有32位地址数据复用AD[3~0]外,还有FRAME、IRDY、TRDY等重要的

- 关键字:

设计 解决方案 接口 PCI CPLD 单片机 基于

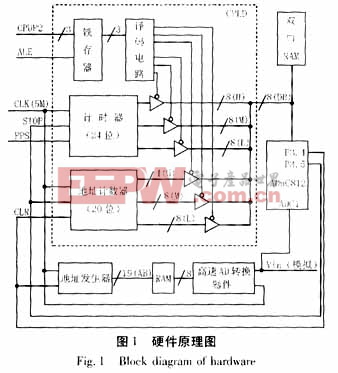

- 高速数据采集系统中精确时标的CPLD实现方法,本文介绍一种利用复杂可编程逻辑器件给高速数据采集系统中的采集数据贴上精确时间标签的方法,并利用MAX PLUSⅡ开发环境验证设计方案的正确性。此设计方案已经成功地应用到自行设计的高速数据采集卡中。

关键词

- 关键字:

CPLD 实现 方法 标的 精确 数据采集 系统 高速

- 在电路设计中,I2C总线是比较常用的两线式串行通信方式,大多数的CPU都擅长于并口操作,不具备直接操作I2C总线接口的能力。为了使不具备I2C总线接口能力的CPU通过对并口的简单操作实现对I2C总线接口的控制,在分析I2C总线常用工作模式的基础上,设计实现工作于主机模式的,以CPID完成I2C总线开始信号、结束信号的输出,以及并行数据到I2C总线模式串行数据转换或I2C模式串行数据到并行数据转换的I2C接口模块。采用该模块,可以使不具备I2C总线接口的CPU通过并口方便地控制I2C总线设备,简化系统程序设

- 关键字:

CPLD I2C 总线 接口设计

- 摘要: 介绍了一种基于CPLD和MT8880的远程控制及语音通信的解决方案。给出了系统的原理框图和关键电路, 并对关键电路的工作原理进行了说明; 最后给出了系统主机控制器中关键模块的QUARTUS II设计图及基于VHDL语言

- 关键字:

CPLD 8880 MT 远程控制

- 引言

检测系统的可重构设计是检测技术的发展方向。可重构设计是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。对于检测系统而言,可重构可以分为软件可重构和硬件可重

- 关键字:

CPLD ARM 可重构 检测系统设计

- 摘要:FPGA可以通过串行接口进行配置。本文对传统的配置方法进行了研究,并从更新配置文件的方法入手,提出了利用处理机通过网络更新的方法,给出了一个用CPLD和Flash对FPGA进行配置的应用实例。

关键词:现场可编程

- 关键字:

Flash CPLD FPGA

cpld/ppga介绍

您好,目前还没有人创建词条cpld/ppga!

欢迎您创建该词条,阐述对cpld/ppga的理解,并与今后在此搜索cpld/ppga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473