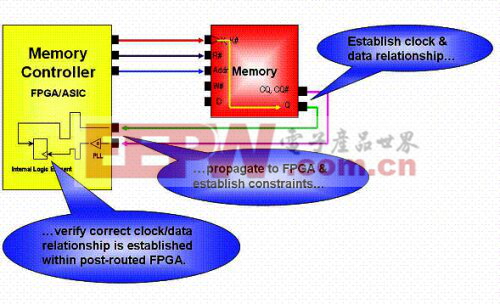

- FPGA设计中的时序管理, 当FPGA设计面临高级接口的设计问题时,该采取什么办法来解决呢?美国EMA公司的TimingDesigner软件可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。下问文将向你娓娓道来。 一、摘要 从简单SRAM接

- 关键字:

管理 时序 设计 FPGA

- 日前,全球可编程平台领导厂商赛灵思公司 (Xilinx, Inc.)宣布推出业界首项堆叠硅片互联技术,即通过在单个封装中集成多个 FPGA 芯片,实现突破性的容量、带宽和功耗优势,以满足那些需要高密度晶体管和逻辑,以及需要极大的处理能力和带宽性能的市场应用。通过采用3D封装技术和硅通孔 (TSV) 技术,赛灵思28nm 7系列FPGA目标设计平台所能满足的的资源需求,是最大单芯片 FPGA 所能达到的两倍。这种创新的平台方法不仅使赛灵思突破了摩尔定律的界限,而且也为电子产品制造商系统的大规模集成提供了

- 关键字:

Xilinx FPGA 堆叠硅片互联技术

- 26年前赛灵思发明了可编程逻辑器件,现在,赛灵思的产品已经遍布无线基础设施当中,特别是在国内TD-SCDMA的部署中,无处不在。FPGA的一个重要价值在于为运营商快速将产品推向市场提供了时间保证,并且FPGA的可编程性使其即使在3G网络部署完成后,仍然能以低成本进行下一代产品升级,提供差异化增值服务。高度集成带有并行DSP处理能力的FPGA还可以以极具成本及功耗优势在BBU、RRU、PTN、GPON/EPON,以及40G/100G以太网中取代ASIC/ASSP。

- 关键字:

FPGA 3G

- 针对目前靶场测试领域尤其是外弹道测试通常采用人工击发枪械的方式,存在安全性差、无法精确控制等问题,设计一种基于CPLD技术的枪械电磁扳机控制仪。采用步进电机作为执行单元,CPLD作为主控制器实现逻辑控制、通信功能。设计中着重考虑了电磁兼容及安全性,通过机械及电气两部分联锁确保控制仪无误触发。通过靶场试验,该控制仪能够适应靶场电磁环境,而且对其他仪器无干扰,其通信功能还可实现整体测试系统的同步性、自动化、网络化及远程控制。

- 关键字:

CPLD 枪械 电磁 控制仪

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

软件无线电 卫星通信 FPGA 模拟源

- 0引言传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内...

- 关键字:

滤波器 FPGA 分布式算法 DSP

- 给出了脉冲位置调制(PPM)系统的设计方案,并基于FPGA通过简明的Verilog代码实现了该设计,时序仿真结果验证了所设计的系统能够满足PPM系统的要求,并在满足一定性能需求的情况下消耗了较少的逻辑资源。

- 关键字:

PPM FPGA 201010

- FPGA在广播视频处理中的应用,1.时机

在世界范围内,广播视频系统的需求都在逐年显著增加,原因是以下的一些因素同时发生了作用:

可供观众选择的广播频道的增加。世界范围内,更多观众的选择从很少的几个频道发展到几百个频道。

- 关键字:

应用 处理 视频 广播 FPGA

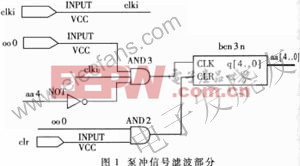

- 利用CPLD实现数字滤波及抗干扰,1 滤波和抗干扰概述

单片机应用系统的输入信号常含有种种噪声和干扰,它们来自被测信号源、传感器、外界干扰源等。为了提高测量和控制精度,必须消除信号中的噪声和干扰。噪声有两大类:一类为周期性的;另一类为

- 关键字:

波及 抗干扰 数字 实现 CPLD 利用

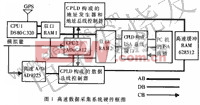

- 基于MAX7000系列CPLD的数据采集系统,CPLD是复杂的PLD,专指那些集成规模大于1000门以上的可编程逻辑器件。它由与阵列、或阵列、输入缓冲电路、输出宏单元组成,具有门电路集成度高、可配置为多种输入输出形式、多时钟驱动、内含ROM或FLASH(部分支持在系

- 关键字:

数据采集 系统 CPLD 系列 MAX7000 基于

- 电子摄像系统已广泛应用于军用及民用测绘系统中,但是效果受到其载体不同时刻姿态变化或震动的影响。当工...

- 关键字:

电子稳像系统 FPGA 图像检测

cpld/fpga介绍

您好,目前还没有人创建词条cpld/fpga!

欢迎您创建该词条,阐述对cpld/fpga的理解,并与今后在此搜索cpld/fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473