- 集成电路按晶体管的性质分为TTL和CMOS两大类,TTL以速度见长,CMOS以功耗低而著称,其中CMOS电路以其优良的特性成为目前应用最广泛的集成电路。在电子制作中使用CMOS集成电路时,除了认真阅读产品说明或有关资料,了解其引脚分布及极限参数外,还应注意以下几个问题。 1、电源问题 (1)CMOS集成电路的工作电压一般在3-18V,但当应用电路中有门电路的模拟应用(如脉冲振荡、线性放大)时,最低电压则不应低于4.5V。由于CMOS集成电路工作电压宽,故使用不稳压的电源电路CMOS集成电路也可以正

- 关键字:

CMOS,集成电路

- 上周五,德科码“CMOS图像传感器芯片(CIS)产业园”项目正式落户南京开发区。该项目总投资约25亿美元,建成后将填补中国CIS产业的空白,主导中国的CIS市场。 图像传感器是数字摄像头的重要组成部分。根据元件不同,可分为CCD(电荷耦合元件)和CMOS(金属氧化物半导体元件)两大类。相机和智能手机的拍照 功能离不开图像传感器芯片,市场很大。但CIS所属的集成电路产业是内地的薄弱产业,芯片目前已超过石油,成为我国第一大进口商品。 “中国必须拥有自己的CIS设计、生产和自主品牌。”香港德科码科技有限

- 关键字:

CMOS CCD

- 2015年11月27日,全球领先的200mm纯晶圆代工厂──华虹半导体有限公司之全资子公司上海华虹宏力半导体制造有限公司(“华虹宏力”)2015年度技术论坛,继9月23日首场在深圳获得热烈反响后,于今日在北京丽亭华苑酒店再度拉开帷幕。来自北京、长三角、西部地区的150多位IC设计精英、知名合作伙伴、行业分析师和媒体朋友齐聚一堂,就产业趋势和市场热点进行了深入交流,并分享了华虹宏力新的技术成果。 公司执行副总裁范恒先生和执行副总裁孔蔚然博士等公司高层亲临论坛现场,与参会嘉宾互动交流。同时公司派出了阵容

- 关键字:

华虹 RF-CMOS

- 长久以来,我国用于高端光学成像的核心元器件一直受制于人。然而,在本月16日在深圳召开的第十七届中国国际高新技术成果交易会(高交会)上,由我国研发的世界上像素分辨率最高、靶面最大的CMOS传感器GMAX3005正式亮相。其以1.5亿像素的超高分辨率,打破了我国一直以来都不具备高分辨率和高灵敏度CMOS图像传感器研发能力的窘境。

图像传感器可以将光信号转化为电信号,是所有成像设备中的核心关键器件。其光电参数直接决定了成像设备的成像质量。今天亮相的GMAX3005拥有着1.5亿像素的超高分辨率,成像速

- 关键字:

CMOS 图像传感器

- 本文讲述运放的参数和选择方面的知识,希望对有需要的读者有帮助。

偏置电压和输入偏置电流

在精密电路设计中,偏置电压是一个关键因素。对于那些经常被忽视的参数,诸如随温度而变化的偏置电压漂移和电压噪声等,也必须测定。精确的放大器要求偏置电压的漂移小于200μV和输入电压噪声低于6nV/√Hz。随温度变化的偏置电压漂移要求小于1μV/℃ 。

低偏置电压的指标在高增益电路设计中很重要,因为偏置电压经过放大可能引起大电压输出,并会占据输出摆幅的一大部分。温度感应和张力测

- 关键字:

运放 CMOS

- 东芝于2015年10月28日正式发布了半导体业务结构改革相关事宜。改革方针有以下几点。

第一,退出CMOS图像传感器业务。将把生产该产品的大分工厂的300mm晶圆生产线及相关资产转让给索尼。完成转让后,该工厂将成为索尼全资子公司——索尼半导体(SCK)的生产基地之一,主要用于生产CMOS图像传感器。

另外,利用300mm晶圆生产线生产的CMOS图像传感器以外的半导体产品将委托SCK生产。随着300mm晶圆生产线转让,与之相关的东芝及其相关公司的员工(大约1100人)

- 关键字:

东芝 CMOS

- 本文介绍了上下拉电阻的作用、使用方法等问题。

重要信号线的上下拉问题

一般说来,不光是重要的信号线,只要信号在一段时间内可能出于无驱动状态,就需要处理。

比如说,一个CMOS门的输入端阻抗很高,没有处理,在悬空状况下很容易捡拾到干扰,如果能量足够甚至会导致击穿或者闩锁,导致器件失效。祈祷输入的保护二极管安全工作吧。如果电平一直处于中间态,那输出就可能是不确定的情况,也可能是上下MOS都导通,对器件寿命造成影响。

总线上当所有的器件都处于高阻态时也容易有干扰出现。因为这时读写控制

- 关键字:

CMOS TTL

- 半导体产业已经因为创投社群对硬件开发领域兴趣缺缺而沮丧了好长一段时间,“超越摩尔定律”有足够的吸引力吗?

- 关键字:

摩尔定律 CMOS

- Sony于8月推出全球首款内建4K录影功能的数位相机α7R II后,将续推高阶α7R系列产品。该系列产品不采用化学低通滤镜(bandpass filter),故图像更为锐利。像素自3,640万提高至4,240万,同时加强自动对焦(AF)与防手震功能。

日本经济新闻(Nikkei)报导,该相机并有399个相位对焦点、5轴图像稳定系统与4K录影等特色,感光值(ISO)最高可达ISO 102,400,结合了高解析、高感光及高速对焦的机种,实际售价约45.1万日圆(约3,800美

- 关键字:

Sony CMOS

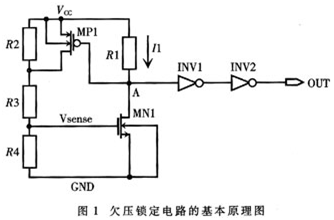

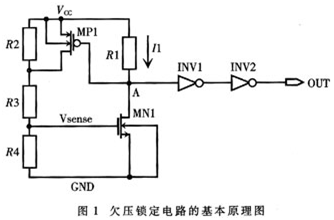

- 在DC-DC电源管理芯片中,电压的稳定尤为重要,因此需要在芯片内部集成欠压锁定电路来提高电源的可靠性和安全性。对于其它的集成电路,为提高电路的可靠性和稳定性,欠压锁定电路同样十分重要。

传统的欠压锁定电路要求简单、实用,但忽略了欠压锁定电路的功耗,使系统在正常工作时,仍然有较大的静态功耗,这样就降低了电源的效率,并且无效的功耗增加了芯片散热系统的负担,影响系统的稳定性。

基于传统的欠压锁定电路,本文提出一种CMOS工艺下的低压低静态功耗欠压锁定电路,并通过HSPICE仿真。此电路可以在1.

- 关键字:

DC-DC CMOS

- 全球领先的高性能模拟IC和传感器供应商艾迈斯半导体公司晶圆代工事业部今日宣布进一步扩展其行业领先的0.35µm高压CMOS专业制程平台。基于该高压制程平台的先进“H35”制程工艺,使艾迈斯半导体能涵盖一整套可有效节省空间并提升设备性能的电压可拓展的晶体管。

新的电压可拓展的高压NMOS和PMOS晶体管器件针对20V至100V范围内的各种漏源电压进行了优化,显著降低了导通电阻,因此可节省器件空间。在电源管理应用中,用优化的30V NMOS晶体管代替固定的50V晶

- 关键字:

艾迈斯 CMOS

- 集成电路按晶体管的性质分为TTL和CMOS两大类,TTL以速度见长,CMOS以功耗低而著称,其中CMOS电路以其优良的特性成为目前应用最广泛的集成电路。在电子制作中使用CMOS集成电路时,除了认真阅读产品说明或有关资料,了解其引脚分布及极限参数外,还应注意以下几个问题:

1、电源问题

(1)CMOS集成电路的工作电压一般在3-18V,但当应用电路中有门电路的模拟应用(如脉冲振荡、线性放大)时,最低电压则不应低于4.5V。由于CMOS集成电路工作电压宽,故使用不稳压的电源电路CMOS集成电路

- 关键字:

CMOS 集成电路

- 现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

因为2.4V与5V之间还有很大空闲

- 关键字:

TTL,CMOS

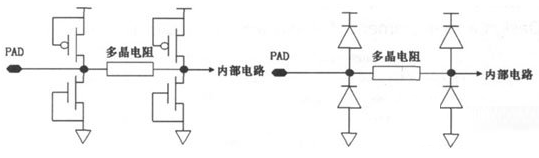

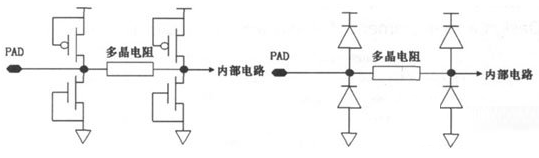

- 简介:大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD 通过PAD导入芯片内部,因此I/O里所有与PAD直接相连的器件都需要建立与之平行的ESD低阻旁路,将ESD电流引入电压线,再由电压线分布到芯片各个管脚,降低ESD的影响。

引言

静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧 厚度越来越薄,芯片的面

- 关键字:

CMOS ESD

- 简介:不断的思考,不断的理解,不断的总结!希望大家坚持下去!

1、CS单管放大电路

共源级单管放大电路主要用于实现输入小信号的线性放大,即获得较高的电压增益。在直流分析时,根据输入的直流栅电压即可提供电路的静态工作点,而根据MOSFET的I-V特性曲线可知,MOSFET的静态工作点具有较宽的动态范围,主要表现为MOS管在饱和区的VDS具有较宽的取值范围,小信号放大时输入的最小电压为VIN-VTH,最大值约为VDD,假设其在饱和区可以完全表现线性特性,并且实现信号的最大限度放大【理想条件下】

- 关键字:

CMOS MOSFET

cmos“介绍

您好,目前还没有人创建词条cmos“!

欢迎您创建该词条,阐述对cmos“的理解,并与今后在此搜索cmos“的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473