现场可编程门阵列(FPGA)器件广泛用于数字信号处理领域.而使用VHDL或VerilogHDL语言进行设计的难度较大。提出一种采用DSP Builder实现FIR滤波器的设计方案,按照Matlab/Simulink/DSP Builder/Modelsim/QuartusⅡ的设计流程,设计一个16阶的FIR低通滤波器,并完成了软硬件的仿真与验证。结果表明,该方法简单易行,可满足设计要求,它验证了采用DSP Builder实现滤波器设计的独特优势。

关键字:

Builder DSP FIR 滤波器

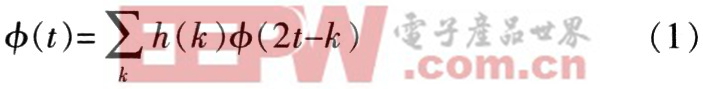

基于DSP Builder的脑电信号小波处理,1 引言

关键字:

小波 处理 电信号 Builder DSP 基于 DSP

设计分析了Chirp函数在时域和频域内的一般特点和解析公式。提出首先在Altera DSP开发工具DSP Builder中实现直接数字合成器(DDS)模块,根据Chirp函数特定的输入/输出(线性和非线性)关系,计算出当前输入字与输出频率的对应关系;然后设计控制字子模块产生DDS模块的频率控制字,驱动DDS产生不同的输出频率,通过在Matlab的Simu-link环境下的仿真验证,得出不同时刻输出的频谱图,验证了该设计能很好地实现Chirp信号源。

关键字:

Builder Chirp DSP 信号源

实现信号源常用的方法是频率合成法,其中直接数字频率合成法是继直接频率合成法和间接频率合成法之后,随着电子技术迅速发展的第三代频率合成技术。DDS是一种全数字技术,它从相位概念出发直接合成所需频率,它具有频

关键字:

Builder FPGA DSP 正弦

1 引言 传统的波形发生器多采用模拟分立元件实现,产生的波形种类要受到电路硬件的限制,体积大,灵活性和稳定性也相对较差。采用FPGA器件直接实现多种波形信号发生器,配以相应的外围器件实现的波形发生器具

关键字:

Builder Matlab DSP 多波形

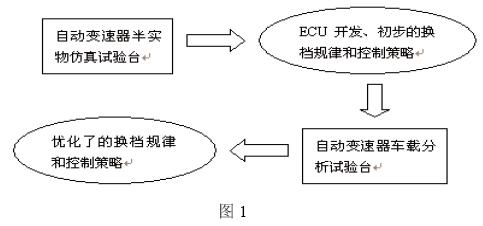

摘要 本文阐述了基于Borland C++ Builder开发的自动变速器电控单元(ECU)实车试验的数据采集系统,通过对系统硬件结构、软件编制核心步骤的描述,详细介绍了系统的开发过程。本数据采集系统为自动变速器电控单元的开发提供了重要的测试平台。

关键词 C++ Builder,电控单元,数据采集,液力自动变速器

1 引言

液力自动变速器是将车速和节气门开度等车辆的状态信号作为电控单元(ECU)的输入信号,经电控单元识别判断处理后,根据换档规律,发出信号给相应电磁阀,利用电磁阀控制油压回路

关键字:

ECU C++ Builder 电控单元 数据采集 液力自动变速器

面向高性能数字信号处理(DSP)设计,Altera公司发布具有第二代模型综合技术的DSP Builder工具8.0。该技术使DSP设计人员第一次能够自动生成基于高级Simulink设计描述的时序优化RTL代码。借助这一新的DSP Builder,设计人员在几分钟内就可以实现接近峰值FPGA性能的高性能设计。和手动优化HDL代码需要数小时甚至数天时间相比,这大大提高了效能。

The MathWorks信号处理和通信市场总监Ken Karnofsky评论说:“DSP Builder是第二

关键字:

Altera DSP Builder RF 嵌入式

数字滤波器在数字信号处理的各种应用中发挥着十分重要的作用,他是通过对采样数据信号进行数学运算处理来达到频域滤波的目的。数字滤波器既可以是有限长单脉冲响应(FIR)滤波器也可以是无限长单脉冲响应(IIR)滤波器。在维纳滤波器理论发明的早期,人们使用IIR滤波器,但现在更多是使用FIR滤波器。本文按照Matlab/Simulink/DSP Builder/QuartusⅡ流程,设计一个FIR滤波器。Altera DSP Builder是连接Simulink和QuartusⅡ开发软件的DSP开发工具。在DSP

关键字:

滤波器 设计 FIR Builder DSP 基于

为帮助系统级设计人员在FPGA软核处理器上有更多的选择,Altera公司(NASDAQ: ALTR)今天宣布,Freescale将为SOPC Builder工具推出32位V1 ColdFire软核。为迅速方便的使用Altera® Cyclone® III FPGA建立系统级设计,设计人员现在使用SOPC Builder工具时,可以选择Freescale®、ARM®或者Altera软核处理器以及50多种其他的知识产权(IP)模块。

SOPC Builder是独特的A

关键字:

Altera SOPC Builder 软核 Freescale FPGA

引言 随着电子技术的发展,VGA(视频图形阵列)接口出现在很多嵌入式平台上,用于图像信息的实时显示等。在某些情况下,设计者希望通过普通的显示器或投影仪观测FPGA内部的一些矢量信号,即把带VGA接口的显示器当作示波器使用等,这就需要对数据进行处理,使之能够在显示器上实时显示。 本文基于DSP Builder的VGA接口设计方法,对VGA接口时序和系统设计需求进行了介绍,并在硬件平台下实现一维与二维信号的显示。 VGA接口标准 VGA显像原理 显示器通过光栅扫描的方

关键字:

DSP Builder VGA 接口 嵌入式系统 嵌入式

摘 要:本文给出了基于Altera DSP Builder平台下VGA接口的系统级设计方法。该接口模块可利用NiosⅡ进行灵活地控制和配置。文中在CycloneⅡ DSP平台上实现了该设计并验证了设计的有效性。

关键词:VGA;DSP Builder;SOPC;行频;场频

引言

随着电子技术的发展,VGA(视频图形阵列)接口出现在很多嵌入式平台上,用于图像信息的实时显示等。在某些情况下,设计者希望通过普通的显示器或投影仪观测FPGA内部的一些矢量信号,即把带VGA接口的显示器当作示波

关键字:

嵌入式系统 单片机 :VGA DSP Builder 行频 MCU和嵌入式微处理器

摘 要:本文从系统总线设计、用户自定义指令和FPGA协处理器的应用这三个方面详细介绍了如何应用SoPC设计思想和SoPC Builder工具来开发电子系统。通过应用SoPC Builder开发工具,设计者可以摆脱传统的、易于出错的软硬件设计细节,从而达到加快项目开发、缩短开发周期、节约开发成本的目的。

关键词:SoPC;SoPC Builder;FPGA 引言 随着技术的进一步发展,SoC设计面临着一些诸如如何进行软硬件协同设计,如何缩短电子产品开发周

关键字:

SoPC Builder FPGA 软硬件设计 系统总线 其他IC 制程

c++builder介绍

您好,目前还没有人创建词条c++builder!

欢迎您创建该词条,阐述对c++builder的理解,并与今后在此搜索c++builder的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473