- 为改善红外图像的视觉效果和后续处理质量,需要对图像进行增强处理。在此介绍并实现了一种空间域图像增强算法,自适应分段线性拉伸算法。首先简要分析算法原理,对该算法基于Xilinx公司XC4VLXl5系列FPGA的实现方法进行了研究,以兼顾系统实时性和集成度为目的,提出灰度直方图统计和拉伸运算等关键模块的解决方案。通过试验结果分析,对压缩因子的选取提出建议。该设计的输出延迟仅为62.-5ns,且具有实现简单、集成度高、功耗低等优点,适合在精确制导武器和导航系统中应用。

- 关键字:

FPGA 图像自适应 分段线性 算法

- 电力系统的频率反映了发电机组发出的有功功率与负荷所需有功功率的平衡情况。高精度和高可靠性的频率测...

- 关键字:

测量 等精度测频 ARM 测控

- 提出了一种基于高频帧摄像头的高频帧实时图像压缩技术,以此技术为基础,使用TMS320CDM642和EP2C35 FPGA相结合,设计了一种高频帧实时图像处理器硬件系统。该系统采用2片SRAM乒乓结构,以及基于TI公司DSP/BIOS和支持XDAIS的JPEG2000压缩算法,实现了100帧/s的压缩速度,系统同时解决了图像压缩中容量和速度的问题,实验了采集和压缩过程的同步进行,大大提高了图像压缩速度。

- 关键字:

FPGA DSP 实时图像 压缩系统

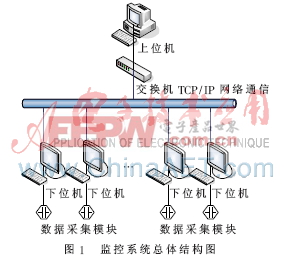

- 基于ARM的城市供水站分布式监控系统, 提出了一种基于嵌入式和TCP/IP协议的三层架构城市供水站分布式监控系统。分析了系统的结构,设计了该系统的硬件,完成了下位机数据采集程序、上位机程序以及系统通信的实现。由此设计出基于ARM(S3C2440A)的高速实时数据采集通信与显示系统,试验验证了该系统良好的可靠性和高速性,具有很好的经济性和实用价值。

- 关键字:

分布式 监控系统 供水 城市 ARM 基于 收发器

- 0引言快速傅里叶变换(FFT)在雷达、通信和电子对抗等领域有广泛应用。近年来现场可编程门阵列(FPG...

- 关键字:

FPGA FFT 移位寄存器

- 1引言当前在EDA领域,只要具备台式或笔记本电脑并装有工具软件,就可以方便地对可编程ASIC(CPLD/FPGA)...

- 关键字:

FPGA ASIC 嵌入式 EDA ISP

- 超长指令字VLIW(VeryLongInstructionWord)微处理器架构采用了先进的清晰并行指令设计[1]。VLIW微处...

- 关键字:

FPGA VLIW 微处理器

- 介绍了一种基于FPGA和DSP的多功能高速数据采集处理系统的设计,该系统的数据采集速度最高可达到105 Msps ,运算能力强,通过更改软件可适用于大部分的高速数据处理场合,具有较强的通用性。

- 关键字:

数据采集 FPGA DSP 201007

- 设计实现了基于FPGA的256点定点FFT处理器。处理器以基-2算法为基础,通过采用高效的两路输入移位寄存器流水线结构,有效提高了碟形运算单元的运算效率,减少了寄存器资源的使用,提高了最大工作频率,增大了数据吞吐量,并且使得处理器具有良好的可扩展性。详细描述了具体设计的算法结构和各个模块的实现。设计采用Verilog HDL作为硬件描述语言,采用QuartusⅡ设计仿真工具进行设计、综合和仿真,仿真结果表明,处理器工作频率为72 MHz,是一种高效的FFT处理器IP核。

- 关键字:

FPGA FFT 移位寄存器 流水线结构

- 从增量型光电编码器的构造特点出发,分析其输出信号中引起抖动误码脉冲的原因。根据编码器两相输出信号(A相、B相)不能同时跳变的特点,设计了一种高精度抗抖动二倍频电路,能有效滤除信号的干扰脉冲。

- 关键字:

FPGA 增量 光电编码器 抖动

arm+fpga介绍

您好,目前还没有人创建词条arm+fpga!

欢迎您创建该词条,阐述对arm+fpga的理解,并与今后在此搜索arm+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473