- 要FPGA与的数字信号采集系统。可以提供大容量的存储空间。提供优秀的系统适应能力。该方案通过计算机并口实现与计算机的通信 ,但是高性能的逻辑分析仪价格昂贵,而且存取深度不足限制了对于海量数字电视信号的分析能力

- 关键字:

SDRAM FPGA 数字电视信号 采集系统

- FPGA MC-CDMA 基带系统 移动通信 摘 要: MIMO技术、多载波技术与链路自适应技术是未来移动通信系统最值得关注的几种物理层技术。MIMO技术在提高系统频谱利用率方面性能卓越,多载波CDMA技术则能有效地对抗频率选

- 关键字:

CDMA 系统 设计 MC MIMO FPGA 空域 复用 基于

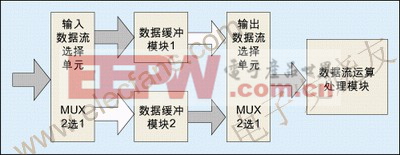

- FPGA/CPLD设计思想与技巧, 本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作中取得事半功倍的效果。

- 关键字:

技巧 设计思想 FPGA/CPLD

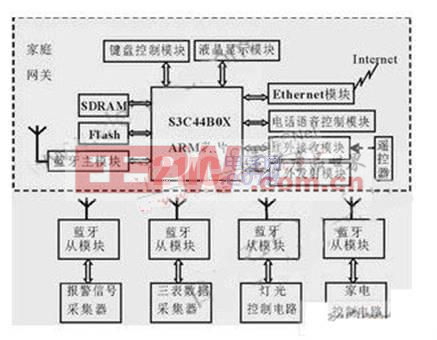

- 基于ARM和uClinux的家庭网关系统,本文以ARM核的32位嵌入式微处理器作为硬件平台,结合无线通信技术,通过移植嵌入式操作系统mClinux,并在其上开发相应的驱动程序、应用程序和嵌入式Web服务器,实现了一个方便、实用的家庭网关。系统的硬件设计系统结

- 关键字:

ARM uClinux 嵌入式

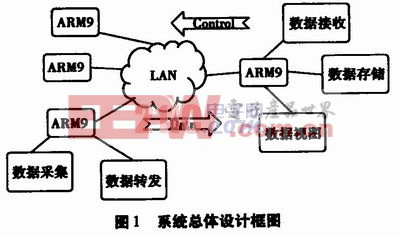

- 基于S3C2410的传感器网络数据采集系统,摘要:针对工业控制中数据采集的需求,设计开发了基于S3C2410的传感器网络数据采集系统,给出了系统的整体设计方案、蛄构框图。整个系统硬件体积小、运行稳定、维护和升级方便。实现了数据采集、传输、处理、量示及控

- 关键字:

数据采集 传感器 ARM

- 摘要:提出了一种基于FPGA 的数字幅频均衡功率放大器的设计方案。系统在完成基于AD620前级小信号放大电路设计的基础上,分析了阻带网络的幅频特性;结合分析结果与FIR 滤波算法给出了相应的滤波器组成方案。后级功

- 关键字:

FPGA 数字 幅频均衡 方案

- 摘要:现代测试领城中,经常需要信号发生器提供多种多样的的测试信号去检验实际电路中存在的设计问题。传统的信号发生器多采用模拟电路搭建。以正弦波信号发生器为例,结合DDS直接数字合成技术,基于FPGA设计其他外围

- 关键字:

FPGA 正弦波信号 发生器

- ARM首席执行官华伦·伊斯特(WarrenEast)在接受媒体采访时表示,该公司不担心英特尔平板电脑芯片的竞争威胁。

伊斯特称,明年平板电脑发货量可能增长至6000万台,其中大多数将配置ARM架构的芯片。伊斯特承认市场上将出现数款配置英特尔芯片的平板电脑,但对它们能否成功持怀疑态度,“目前,凌动芯片在能耗方面的表现不够好,英特尔清楚这一点”。

苹果iPad是平板电脑市场上的霸主,配置ARM架构的芯片。市场研究公司StrategyAnalytics最近称

- 关键字:

ARM 平板

- 多相滤波是实现数字下变频及数字相干检波的关键技术,是雷达、声纳和通信等系统中为数字信号处理提供高质量的正交信号的有效手段。文中讨论了多相滤波的基本原理,给出了采用多相滤波的方法对中频带限信号处理的仿真分析,并结合一款脉冲压缩雷达中频数字化接收机的实现方案进行工程验证,结果表明,在技术指标上可有效克服正交通道不一致问题,具有较高的应用价值。

- 关键字:

FPGA 多相滤波 数字 相干检波

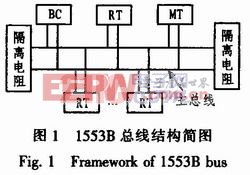

- 基于DSP的1553B总线系统设计与实现,摘要:在研究1553B总线协议特点的基础上,提出了一种基于DSP的1553B总线接口设计方案.详细描述了硬件电路的实现及软件驱动程序的编写。在电路中采用DSPTMS320F2812为核心处理单元。BU-64843为1553B协议执行元件,采

- 关键字:

DSP FPGA

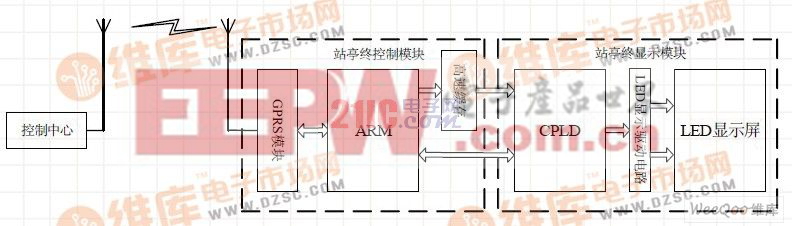

- 基于ARM7和CPLD的数字公交站亭系统设计, 摘要:提出了一种基于ARM7 和CPLD 架构的数字公交站亭系统。系统通过GPRS 模块与公交控制中心实时通信,使用CA 认证保证通信的安全性,采用两块SRAM 组成具有“乒乓逻辑”的高速缓存确保显示数据的连续性

- 关键字:

ARM DSP CPLD

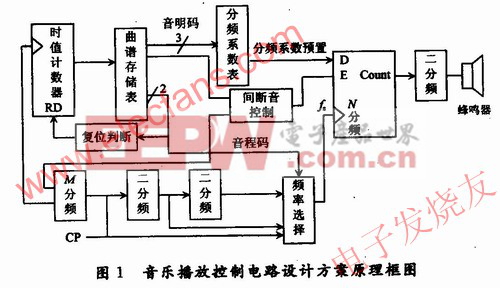

- 基于FPGA的音乐播放控制电路设计, 随着电子技术发展,电子电路的形式趋向复杂化,面对这一状况,人们已经清醒地认识到,要分析和设计复杂的电子系统人工的方法已不适用。依靠传统的实验教学已远不能满足社会对高新技术人才的培养需要。本文就一个

- 关键字:

控制 电路设计 播放 音乐 FPGA 基于

- 基于FMC标准的FPGA夹层卡I/O设计, 面对似乎层出不穷的新 I/O 标准,目前嵌入式系统设计人员继续依靠 FPGA 来部署系统日益重要的外部 I/O 接口,这点丝毫不足为奇。FPGA 可提供大量可配置的 I/O,能在适当 IP 基础上支持几乎无限多种高度复杂的 I/O

- 关键字:

I/O 设计 夹层 FPGA FMC 标准 基于

- 采用90nm工艺制造的DDR3 SDRAM存储器架构支持总线速率为600 Mbps-1.6 Gbps (300-800 MHz)的高带宽,工作电压低至1.5V,因此功耗小,存储密度更可高达2Gbits。该架构无疑速度更快,容量更大,单位比特的功耗更低,但问

- 关键字:

SDRAM FPGA DDR3 存储器

arm+fpga介绍

您好,目前还没有人创建词条arm+fpga!

欢迎您创建该词条,阐述对arm+fpga的理解,并与今后在此搜索arm+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473