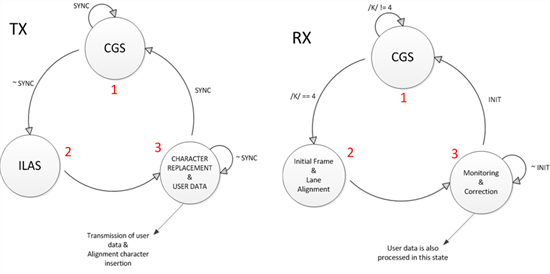

在使用我们的最新模数转换器 (ADC) 和数模转换器 (DAC) 设计系统时,我已知道了很多有关 JESD204B 接口标准的信息,这些器件使用该协议与 FPGA 通信。此外,我还在 E2E 上的该栏目下阅读了各种技术文章及其它博客文章,明白了为什么 JESD204B 是 LVDS 和 CMOS 接口的后续产品。

有一个没有深入讨论的主题就是解决 ADC 至 FPGA 和 FPGA 至 DAC 链路问题的协议部分,这两种链路本来就是相同的 TX 至 RX 系统。作为一名应用工程师,我所需要的就是

关键字:

JESD204B FPGA DAC

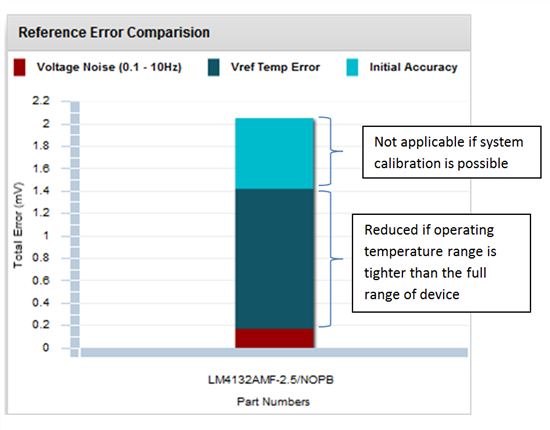

您是否知道至少一个可用于几乎每个应用的电压参考?这是因为在系统信号链内某个地方总需要一个参考点。电压参考大多数用作数据转换器基准,但也可用于很多其它方面,例如比较器阀值和齐纳二极管替代方案等。由于这类器件引脚数量极少(一般 3-5 个引脚),因此我们通常对这一部分只是粗略带过,但如果未正确选择该组件,它就很容易成为系统的“问题小孩”。

图 1 — 参考总误差实例以及它如何随工作条件变化而变化

此外,市场上有大量的参考产品,其中

关键字:

电压 齐纳二极管 ADC

Analog Devices, Inc. 近日宣布推出业内速率最快的16位高温ADC AD7981,这款器件的速率相当于市场上现有转换器的两倍以上,可在最高175摄氏度的高温环境下无错运行。

AD7981 PulSAR® ADC的采样速率高达600 kSPS,是包括宽带宽声音测量和振动测量以及带宽较低的低功耗压力检测和温度检测等应用的理想选择。 AD7981可根据采样速率调节功率,从而在恶劣环境中最大限度地延长电池寿命,在600 kSPS全速模式下功耗仅4.6

关键字:

ADI ADC AD7981

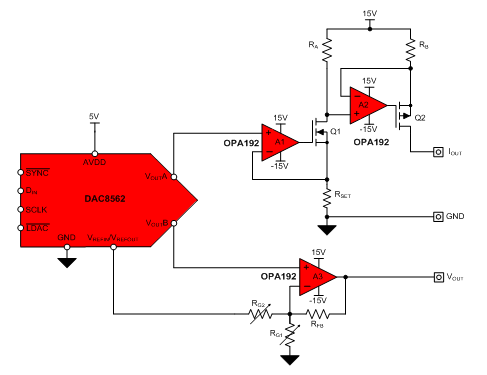

图 1

图 1 是 3 线模拟输出模块图。该模块使用双通道 DAC8562 数模转换器 (DAC) 驱动支持高电压、36V OPA192 运算放大器的电压与电流输出级。

电流输出是一个双级、高侧、电压至电流转换器。由放大器 A2、MOSFET Q2 和检测电阻器 RB 组成的第二级电路可为负载提供输出电流。A2 可在反相输入节点上感测整个 RB 上的压降,从而可通过负反馈调节输出电流。这样可确保其等于应用在非反相输入端的电压。

如果单独使用该级,高侧电源上

关键字:

德州仪器 DAC 电流转换器

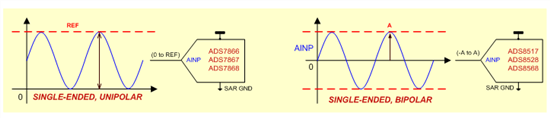

您是否知道输入信号可能会影响为应用选择最佳逐次逼近寄存器 (SAR) 模数转换器 (ADC) 的方式?

在我们听到“输入”两个字时,脑海里会立即浮现频率、幅值、正弦波以及锯齿波等几件事。所有这些都是优化信号调节时需要考虑的相关问题。

但是,很多人不会预先考虑的一件事是 SAR ADC 的实际输入类型。在本博客中,我将重点介绍三种 SAR 输入(单端、伪差分与差分输入)以及如何将其使用在应用中。在以后的博客中,我还将讨论性能差异以及获得最优输入性能所必须考虑的一些重要

关键字:

SAR ADC 全差分

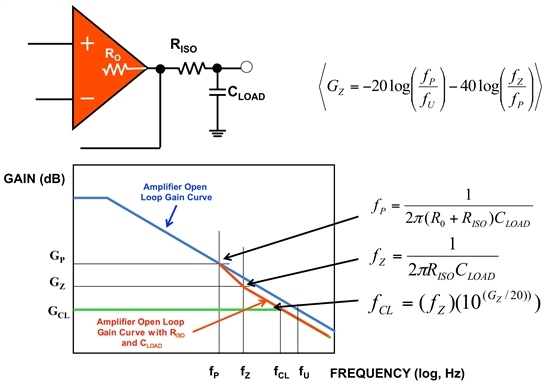

他们说如果使用放大器驱动电容负载(图 1、CLOAD),一个不错的经验是采用一个 50 或 100 欧的电阻器 (RISO) 将放大器与电容器隔开。这个附加电阻器可能会阻止运算放大器振荡。

图 1.支持电容负载的放大器可能需要在放大器输出与负载电容器之间连接一个电阻器。

使用 50 或 100 欧姆 (RISO) 电阻不一定每次都管用。问题是,“如果 CLOAD 超过产品说明书中推荐的运算放大器电容负载值时该怎么办?”

如果您无法找

关键字:

运算放大器 电容 ADC

凌力尔特公司 (Linear Technology Corporation) 推出高压侧或低压侧采样的电荷、功率和能量监视器 LTC2946,用于 0V 至 100V DC 电源轨范围。集成 ±0.4% 准确度的 12 位 ADC 和精确的外部时基 (晶体或时钟) 可实现优于 ±0.6% 的电流和电荷测量准确度、以及 ±1% 的功率和能量测量准确度。在没有外部时基时,准确度为 ±5% 的内部时基可以取而代之。所有数字读数 (包括电压、电流和功率的

关键字:

凌力尔特 ADC LTC2946

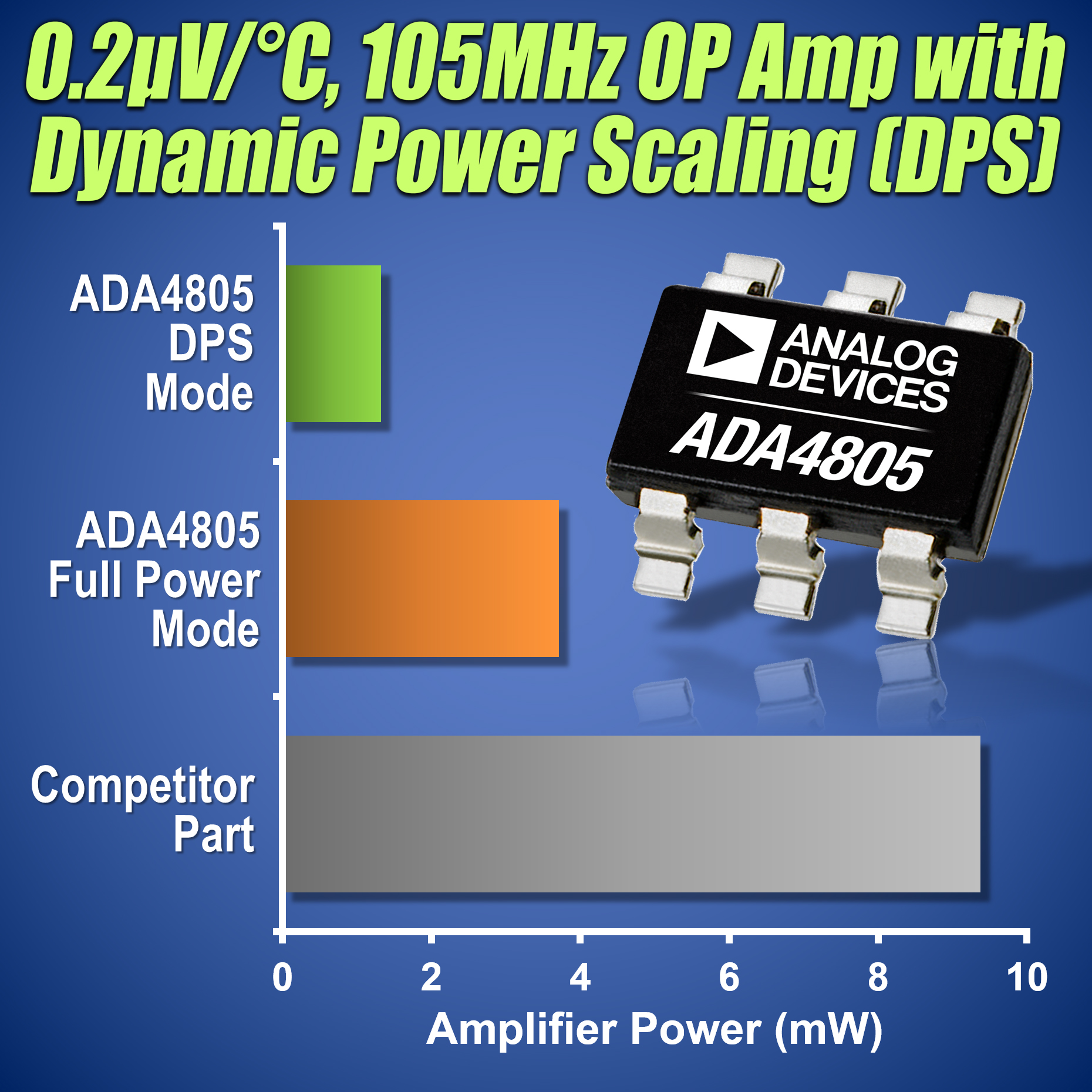

Analog Devices, Inc. ,全球领先的高性能信号处理解决方案供应商,近日面向要求超高精度和能效的高速数据采集系统推出低功耗轨到轨放大器ADA4805-1和ADA4805-2。 对于寻求实现高分辨率ADC数据手册规定的全部潜力的系统设计师来说,ADA4805-1(单通道)和ADA4805-2(双通道)放大器是静态电流低至495µA的唯一解决方案。 放大器的动态功耗调节(DPS)特性允许用户在ADC采样之间关闭放大器,实现对功耗的动态管理。 与类似解决方案相比,该技术可使其功耗

关键字:

Analog Devices ADC 放大器

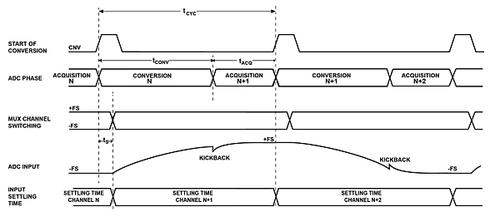

通过多路复用,每个系统可以使用更少的ADC,从而显著节省功耗、尺寸和成本。 逐次逼近型ADC(因为其采用逐次逼近型寄存器而常常称为SAR型ADC)具有低延迟特性,很受多路复用系统的欢迎——这些系统要求对满量程输入步进(最差情况)做出快速响应,而不会产生任何建立时间方面的问题。 SAR型ADC易于使用,功耗很低,并且尺寸较小。

本文重点讨论采用高性能精密SAR型ADC的多路复用数据采集系统的重要设计考虑、性能效果和应用挑战。

切换多路复用器的输入通道时,ADC驱动放大

关键字:

数据采集系统 ADC 寄存器

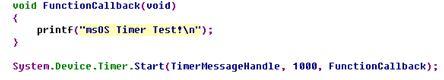

注册机制在嵌入式编程中很少提到,但回调函数大家经常接触,以软件定时器为例:

软件定时器设备通过函数Start把FunctionCallback作为参数传入定时器设备中保存,之后开启定时器,延时1000ms之后,定时器就会直接调用FunctionCallback,所以这个FunctionCallback就叫做回调函数。类似处理器的中断一样。

注册机制类似回调函数性质,只是把概念扩展到变量,上层应用通过注册函数地址或者变量地址到设备中保存,当设备中这个地址对应的函数

关键字:

嵌入式微系统 注册机制 ADC

凌力尔特公司 (Linear Technology Corporation) 推出 16 位 2.5Gsps 数模转换器 (DAC) LTC2000,该器件具出色的频谱纯度,在 200MHz 输出时 SFDR 为 74dBc,输出频率从 DC 至 1GHz 时 SFDR 优于 68dBc,这比同类的 14 位 DAC改进了 12dB。LTC2000 具低相位噪声和很宽的 2.1GHz -3dB 输出带宽,在高端仪表、宽带通信、测试设备、有线电视 DOCSIS CMTS 以及雷达应用中,能够实现宽带或高

关键字:

凌力尔特 DAC LTC2000

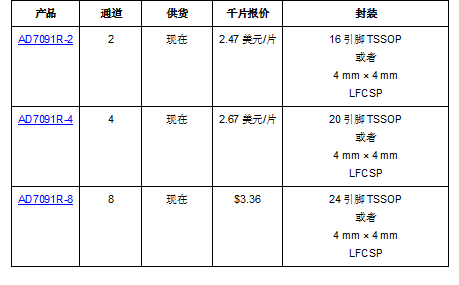

Analog Devices, Inc. (ADI)近日推出三款超低功耗多通道12位1 MSPS SAR(逐次逼近型寄存器)ADC AD7091R-2、AD7091R-4、AD7091R-8。这三款新型2通道、4通道和8通道ADC专门针对电池供电的数据采集模块、手持式计量表、现场仪器仪表、通信应用以及便携式心电图仪、心率监护仪等医疗设备而设计。三款ADC在同类产品中具有最高能效,1 MSPS(百万采样/秒)时最大功耗为1.7 mW,比最接近的SAR ADC竞争产品低60%以上。这些ADC采用微型4 m

关键字:

ADI ADC 采集模块

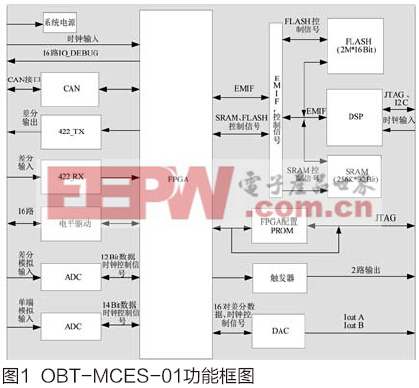

摘要:本文在SIP立体封装技术的基础上,设计了基于DSP、FPGA的复合电子系统模块。重点介绍了模块的功能构成及模块接口应用,为基于SIP小型化封装的复合电子系统(功能可订制)提供应用基础。

引言

随着电子技术的发展对系统模块小型化高可靠性提出了更高的要求。复合电子系统模块是欧比特公司推出的一款SIP模块,其将特定(可定制)的电子系统功能模块采用立体封装技术制作而成。本文介绍了基于DSP、FPGA的复合电子系统模块OBT-MCES-01的功能构成以及应用方法。

1 SIP简介

关键字:

复合电子系统 DSP FPGA ADC DAC RS422 CAN 201409

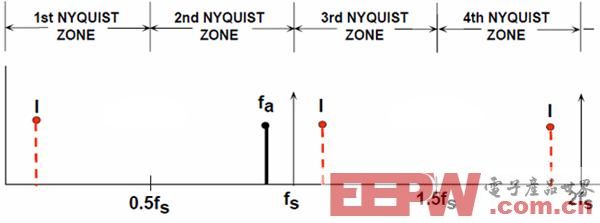

许多数字处理系统都会使用FPGA,原因是FPGA有大量的专用DSP以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA都要和高性能的ADC和DAC进行接口,比如e2v EV10AQ190低功耗四通道10-bit 1.25 Gsps ADC和EV12DS130A内建4/2:1 MUX的低功耗12-bit 3 Gsps DAC。 通常情况下,这些转换器的采样率都达到了GHz的级别。对工程师团队来说,除了混合信号电路板布局之外,理解和使用这些高性能的设备也是一个挑战。

关键字:

ADC DAC FPGA

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

运算放大器 ADC DC/DC 完全隔离式 数据采集

adc-dac介绍

您好,目前还没有人创建词条adc-dac!

欢迎您创建该词条,阐述对adc-dac的理解,并与今后在此搜索adc-dac的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473