ADC采样率与信号频率:关键概念与设计要点

ADC采样率与信号频率:关键概念与设计要点

在模数转换器(ADC)的设计与应用中,采样率与信号频率的关系是影响系统性能的核心因素。采样率是指ADC对模拟输入进行采样的速度,通常由外部时钟或内部锁相环(PLL)提供。现代高速ADC常采用JESD204B标准接口,采样率可达数GHz,但实际数据速率往往需要通过抽取或内插技术进行调整。

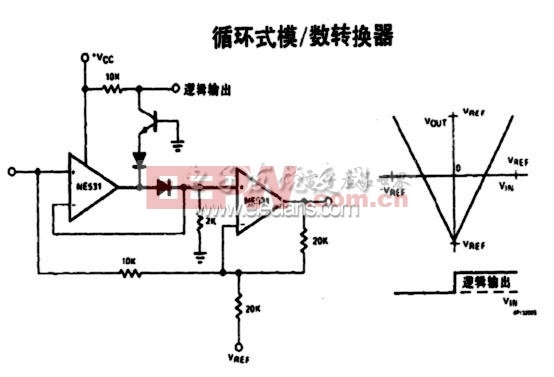

采样率与奈奎斯特准则

根据奈奎斯特采样定理,ADC采样率必须至少是信号最高频率的两倍。但在实际工程中,推荐采样率为信号带宽的2.5倍以上,以避免频谱混叠。例如,对于300MHz带宽的信号,理想采样率应不低于750MSPS。

频率规划的重要性

合理的频率规划可以避免信号谐波与采样镜像的重叠。通过调整采样率,可以移动频谱中杂散的相对位置。例如,当4GSPS采样的ADC出现谐波重叠时,将采样率提高到5.5GSPS可能完全消除重叠,显著改善系统性能。

分辨率与采样率的权衡

ADC的分辨率(位数)直接影响采样率上限。高分辨率ADC需要更长的建立时间(Settling time)来确保信号稳定在1/2LSB范围内。12位ADC的建立时间通常是时间常数的8.4倍,这限制了其最高采样率。因此,在需要高采样率的应用中,可能需要适当降低分辨率要求。

带宽与采样保持电路

ADC的带宽(Full Power Bandwidth)主要由采样保持电路中的RC特性决定。例如,2.5GSPS的12位ADC需要约6.62GHz的带宽。采样保持电路的工作模式(采样/保持)及其瞬态响应(Acquisition time, Settling time等)共同决定了ADC的实际带宽能力。

抽取与内插技术

现代ADC/DAC常采用数字下变频(DDC)和数字上变频(DUC)技术。抽取通过降低数据速率来减轻系统负担,例如1GSPS采样率在抽取因子为4时可输出250MSPS数据。内插则用于提高有效采样率,通过在采样点间插入零值并滤波实现。这些技术使系统能在保持高采样率的同时,降低对数字接口的速度要求。

实际应用建议

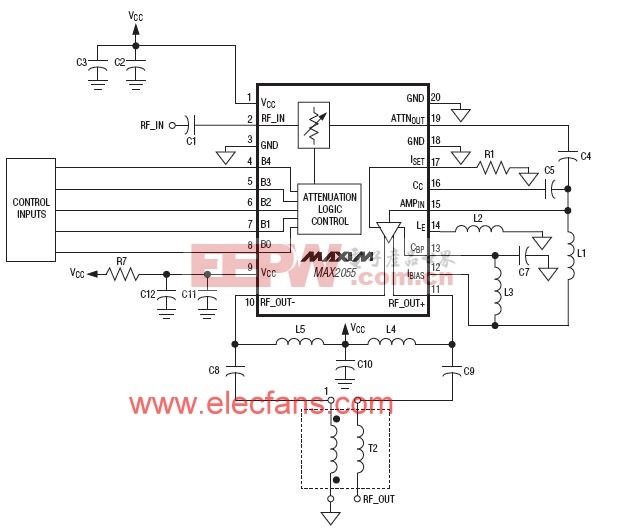

l 对于射频中频接收等高频应用,优先关注ADC带宽指标

l 对于传感器信号采集,重点考虑采样率与信号带宽的关系

l 使用频率规划工具优化采样率选择,避免谐波干扰

l 在高速系统中,考虑采用JESD204B接口和抽取/内插技术平衡性能与复杂度

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。